主题中讨论的其他部件: DAC5687, DAC5688

尊敬的任何能帮我解决问题的人

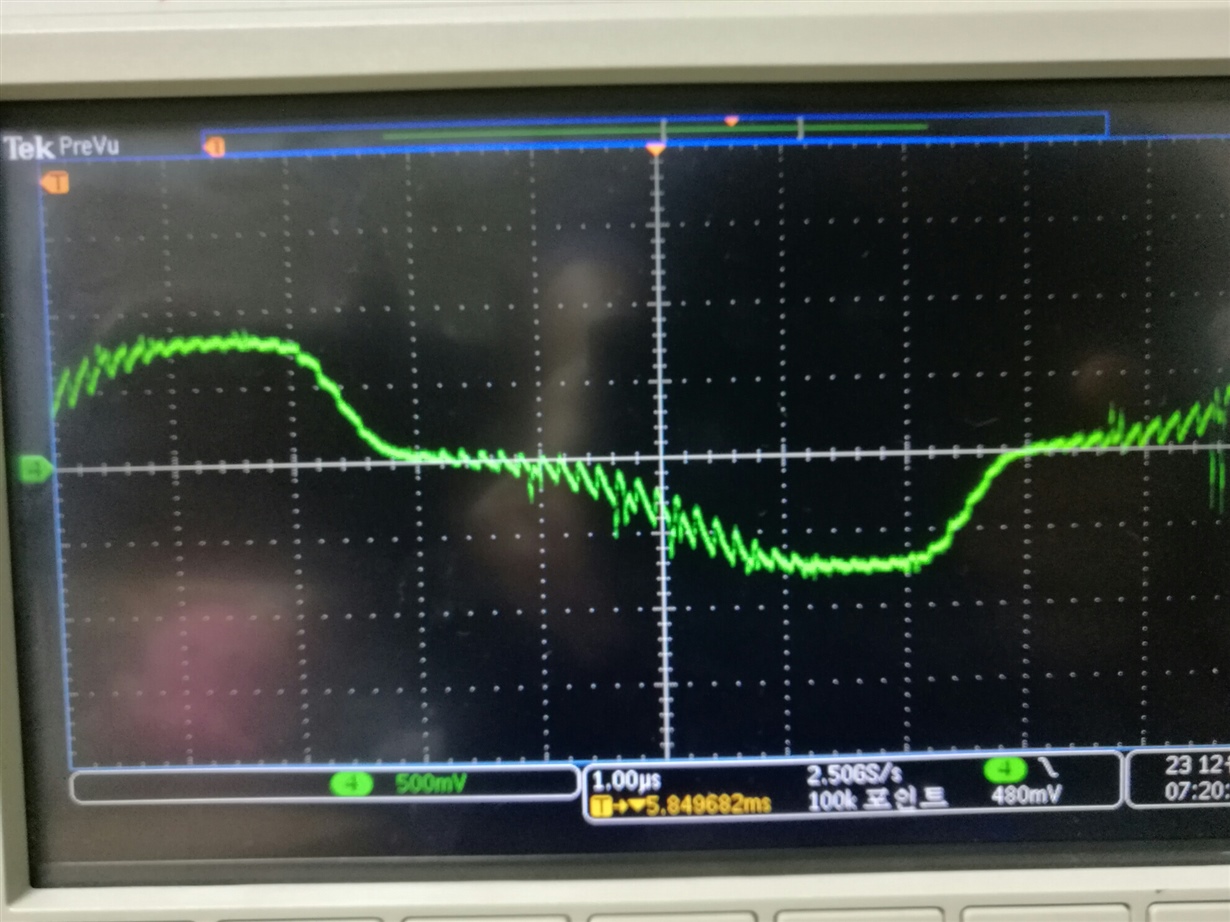

我在定制电路板上使用DAC3482已有几天,但所有的试用都被发现失败。 测试条件和观察到的结果如下所示。

1.测试条件

1)操作参数

-数据时钟:100MHz

- DAC时钟:100MHz (外部,无内插(1x)且NCO已禁用)

- FIFO同步:单同步源模式,与非周期帧同步(双模式也经过测试,但结果相同)

-数据格式:Word格式

-测试输入:频率1亿/1024Hz(=97.66kHz)处1024处的正弦波

2)注册设置和配置顺序

注册 值

0 0x009C

1 0x000E

2 0xF082

3 0xA000

7 0xD8FF

12 0x0400

13 0x0400

20 0x0000

21 0x5000

24 0x2808

26 0x0020

27 0x0800

9. FIFO偏移(正确选择,不会发出FIFO碰撞警报)

31 0x1110

32 0x2201 (且TXENABLE变为高)

5 0x0000 (循环最后4行,直到不再发生FIFO冲突)

结果

1)始终发生报警FIFO 1或2 AWA以外

2)输出波形严重失真(

3)锯齿形状周期,在观察到的输出中为16个数据时钟周期

4) 拍摄的照片(请查看信封,但不要介意小故障,因为我认为以后可以通过调整时钟相位来处理小故障)

感谢您的关注!

此致,

垫片