主题中讨论的其他部件: ADS7042, ADS7854

您好!

这是我的Verilog HDL代码: http://paste.org.ru/?x2a6yj

我尝试使用ADS8881 ADC,但它的接口经常被卡住。 FPGA是Xilinx XC6SLX9,时钟速度为140 MHz (可满足ADS8881的70 MHz最大时钟速度)。 采样率为500 KHz,信号为525 KHz正弦。 每20-50 us接口就会挂起,我会重新启动循环。 字节联动接口I是指ADC对控制信号没有反应。 在循环重启后,我看到它继续按预期工作,然后在20-50 us后,错误再次重复出现=(

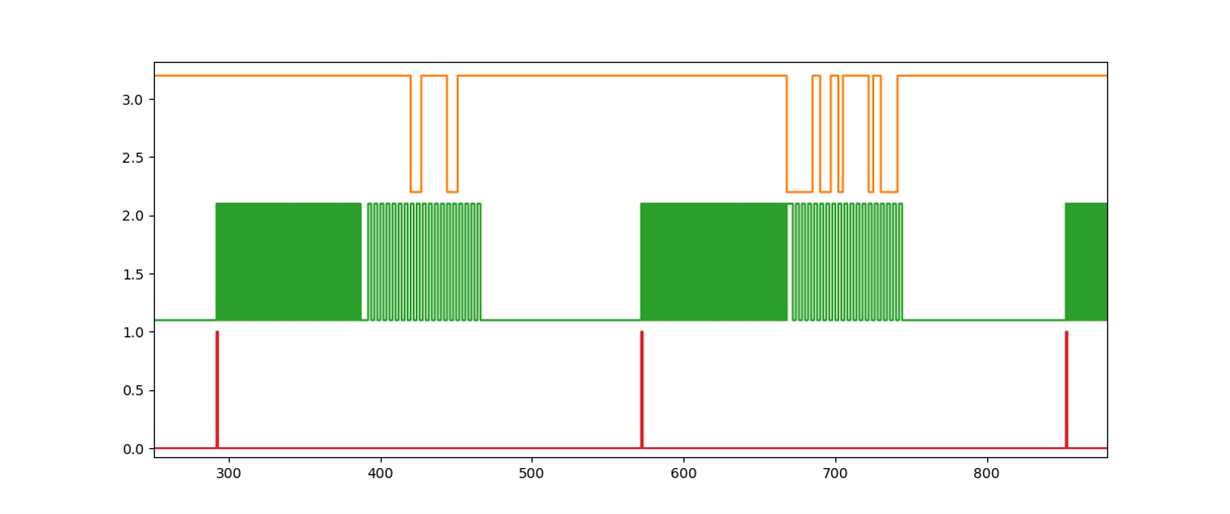

我还看到另一个错误(请看下面图片的左半部分:DIN=1,dout =橙色,SCLK =绿色,convst=红色)-有时我的模块开始错误地捕获数据,但dout错误地返回到级别1。 图的右半部分显示正常循环,无错误。

我尝试了数据表中的多种模式:3线4线,都有忙或没有忙,然后发现ADC工作不稳定。 这让我哭了,我做错了什么? Xilinx ISIM和Modelsim中的建模显示,我的代码一切正常-许多不同的度量方法都是随机18位值,随机转换时间从500到700 ns -在HDL模拟器中都可以,但在实际ADC =()中则不行

可能有人可以将他的代码分享给我和所有其他人? 如有需要,我可以提供更多的细节。 请帮助,我花了很多周时间让它稳定运行。 我可以尝试更多的调试理念?