主题中讨论的其他部件: INA827, TM4C1294NCPDT, REF5045

尊敬的各位:

我正在使用4通道 Δ-Σ ADC的ADS131A04应变仪放大器设计。 对于我的应用,总共需要12个通道,但板面积有限,因此我设计了一个具有4个通道的小型可堆叠板。 其中三块板插入主电路板,带有用于信号处理的TM4C1294NCPDT。 通过SPI读出ADC的效果非常好。 但是,在检查信号时,我注意到一些ADC的所有4个通道都存在奇怪的干扰,其形式为低频振荡,每隔几秒定期发生一次。 信号向上摆动至0.5 -2mVpp,然后再次淡出。 由于来自应变仪放大器(INA827)的测量信号也在mV水平上,因此这种干扰是不可取的。 由于其性质,我相信也不可能过滤。

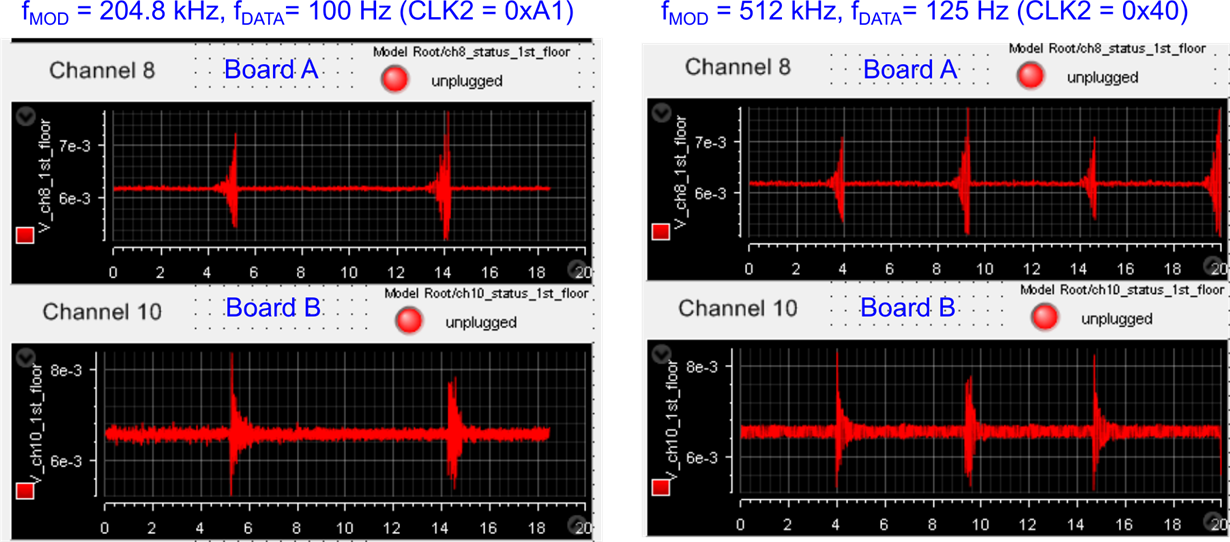

我怀疑我看到的是真伪声调/Δ-Σ ADC的限制周期。 这是因为当我更改ADS131的调制器采样速率时,在给定期间内获得的干扰数会相应地进行标度。 更改调制器与输出采样率的比率时,干扰的特性会发生变化。 图中的Y轴以V为单位,时间刻度以秒为单位。

鉴于我的假设是正确的,仍有一些我不理解的影响:

- 如果只插入主板上的一个小板,则不会发生干扰。

- 每3块板中就有一块不会显示主板上任何可能的单个板组合的干扰。

- 将其中一个"坏"板与"好"板结合会导致不同形式的干扰。

- 将这两个"坏"的插座结合在一起总是会产生我所批评的干扰,但特性会稍有变化,具体取决于主板上使用的插座。

- 正如您在图片中所观察到的,干扰会在电路板之间的时间上发生变化,并且会以某种方式"镜像"

1)可能是由于添加另一个板时电源电流/电容增加而导致的整体噪声级别变化所致。

2)可能是由于生产过程中的变化(?)

至于其他效果,我不知道。 我们非常感谢您提供任何建议/帮助/意见。 我需要知道干扰的来源以及避免干扰的策略,然后再制造更多的PCB,而这些PCB最终对我的应用毫无用处。

每个正ADC通道的输入来自INA827仪表放大器的输出级。 负极输入连接到接地。 ADS131的AVCC/AVSS和IOVDD/IOVSS绑定到同一电源。 使用(非缓冲)外部电压参考REF5045。 图中的相关部分随附,供您参考。

由于这是我的第一个职位,我希望我提供所有必要的细节。 如果您需要了解有关电路,系统设置,电源或其他方面的其他信息,请告诉我。