线程中讨论的其他部件: LMK0.461万, LMX2572, LMX2582, ,LMK0.4828万, LMX2594, TRF3765

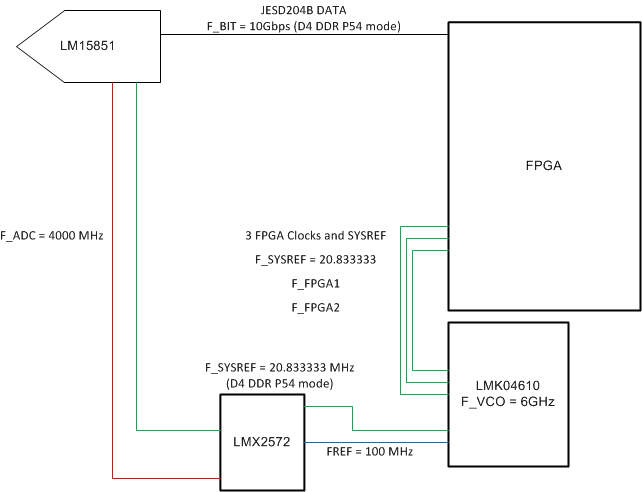

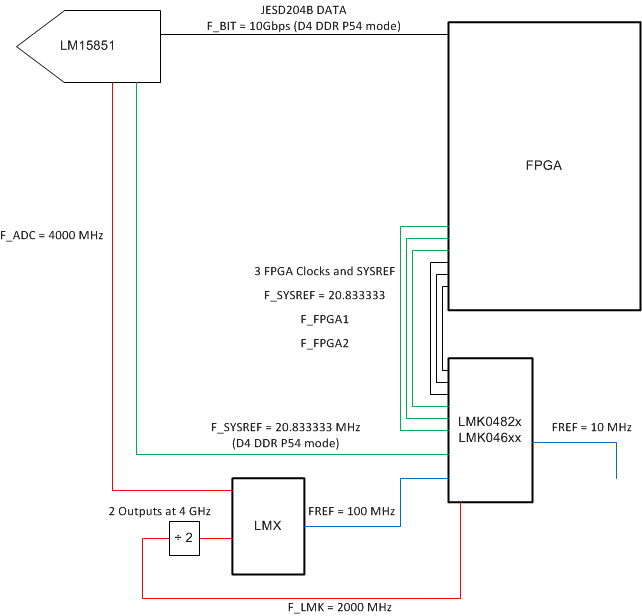

您好! 我需要为LM1.5851万提供4GHz设备时钟+ SYSREF,以及FPGA提供其它设备时钟+ SYSREF (JESD204B系统)。 如我所见,没有合适的时钟解决方案集成到单个IC中,具有如此高的输出频率和JESD204B支持。 因此,LMK0.461万和LMX2572级联似乎是合适的。 您是否愿意对使用这些设备的时钟架构做出一些解释? 两个时钟设备应如何连接在一起,以及如何与LM1.5851万和FPGA连接? 什么是SYSREF信号架构?

也许有更多合适的设备,但这两种设备是由于其低功耗而被选中的。 也许您可以推荐其他设备。 提前感谢。