你(们)好

我正在使用ADS1291测量手腕心电图。

目前,我将其设置为500 SPS并收集数据。

我在30秒内就完成了测量,但我得到了4.1万 数据。

我认为SPS = Hz。

所以我认为如果我们测量500 SPs和30秒,我们应该得到1.5万 数据。

我想知道我错了。

请帮帮我。 谢谢你。。。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

非常感谢您使用TI的产品。

此TT已收到/查看,我将在3~5天内返回给您。

我是否可以提出更多问题来收集更多详细信息?

您是否 使用任何评估套件/电路板?

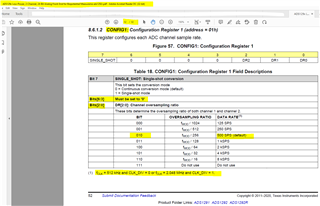

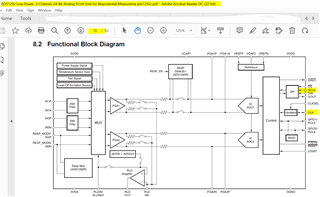

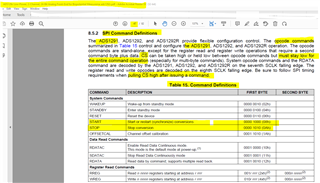

根据“ADS129x低功耗,2通道,24位模拟前端,用于双电位测量数据表(修订版 c)",

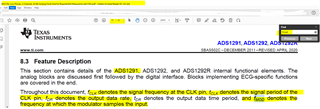

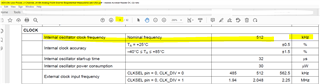

您正在使用/设置什么时钟和CLK_DIV?

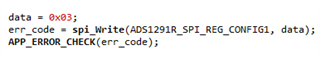

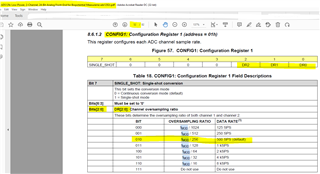

您是否在config1寄存器中写入了正确的值?

同时,让我与我们的工程师团队回顾一下。

感谢。

你(们)好

感谢您的回复。

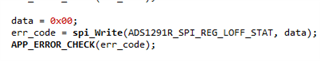

我检查了您指出的部分。

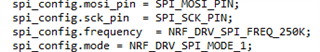

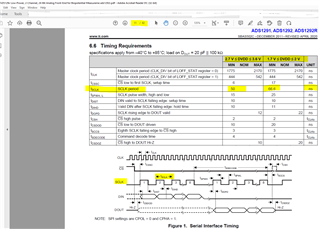

我的SPI频率为250kbps。

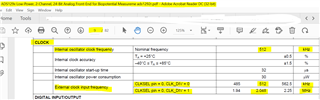

因此,fCLK是250kbps (1Hz = 2bps,250kbps = 500kHz是这样吗?)

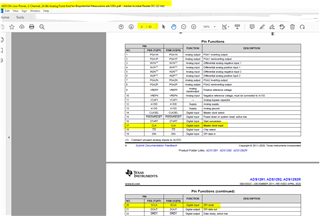

我 将CLK_DIV位设置为0。

因此,闪存模块= fCLK/4 = 125kHz

我想要500Hz,125k / 250 = 500Hz。

将DR0设置为DR2位0,1,0

我就是这样做的。 对吗?

谢谢你。

您是否 使用任何评估套件/电路板?

我建议首先检查时钟输入-

请检查您使用的是哪个时钟? 内部还是外部? 如果可能,请使用示波器探头检查CLK引脚的时钟频率吗?

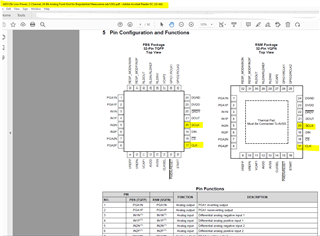

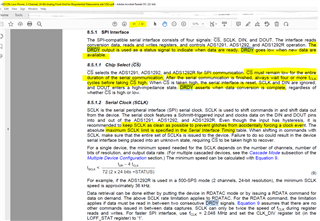

CLK引脚是一个输入(如果使用外部时钟)引脚,用于连接/提供外部时钟(来自主机(uController/FPGA)的晶体振荡器或方波)以提供时钟。

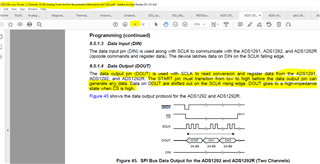

SCLK是SPI通信的输入引脚,应来自主机(uController/FPGA)。

请注意,CLK与SCLK不同。

仔细检查以下各项并相应地进行设置以满足时钟源(外部或内部)-

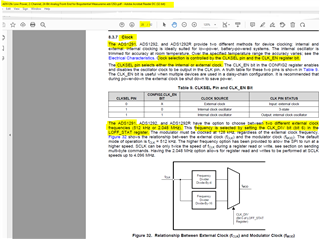

时钟选择由CLKSEL输入引脚和CLK_EN寄存器位控制。

CLKSEL针脚选择内部或外部时钟。 CONFIIG2寄存器中的CLK_EN位启用

并禁用要在CLK引脚中输出的振荡器时钟。

此外,它是否可能以您设置的正确速率进行采样,但主机读取的数据块更长/更大,以便显示?

您可以通过注射 已知 数量的低频,低振幅 正弦波或使用Fluke生物医学 患者监视器模拟器来测试/验证这一点。

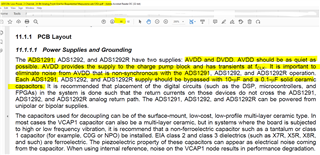

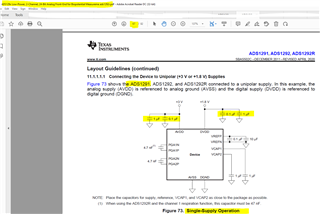

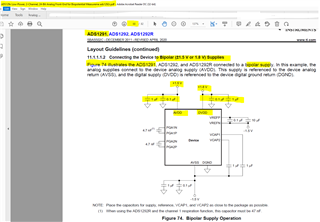

AVDD,AVSS和DVDD的电压读数是多少?

您能否仔细检查VDD和VSS是否安静且干净?

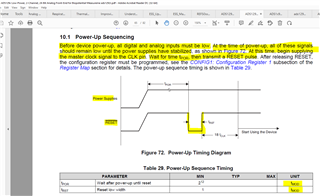

另外,您是否可以检查正确的开机顺序-

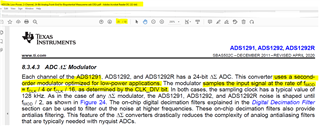

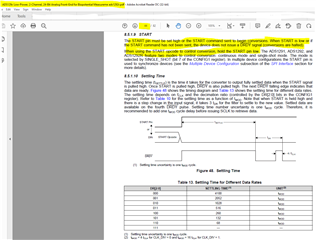

从您提供的原理图中,它使用内部时钟512 kHz。

您是否可以尝试写入CONFIIG2寄存器的1到3位(CLK_EN)并使用示波器检查CLK引脚是否为512kHz时钟?

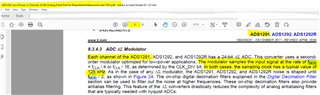

采样时钟的典型值为128 kHz;因此采样速率与数据速率不同。

如果将010写入DR[2:0],采样率仍为128kHz,数据速率将为128K/256=500 SPS。

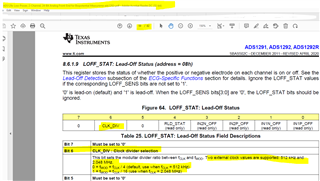

请探头检查SCLK信号是否清洁且安静。 您的SCLK频率是多少?

您可能需要在数据传输过程中使用示波器探测以下内容(从设备读取/写入设备)-

取决于DVDD电源电压,SCLK周期需要长于50或66.6 ns -

请问您的SCLK周期或频率是多少?

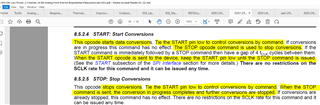

在原理图中,起始针脚连接到低电平,因此需要发送起始命令 以开始转换。

如果可能,我可以看到CLK,/CS,SCLK,/DRDY,DIN, 当您读取数据时,您会如何?