Other Parts Discussed in Thread: ADS58C48

在“线程: LMK0.4828万”中讨论的其它部件

大家好,

以下是 一位客户提出的问题。

目前,它可以与ADS58C48正常通信。 FPGA端配置为DDR LVDS模式。

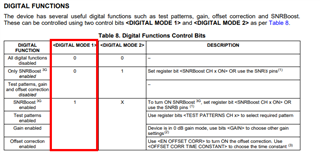

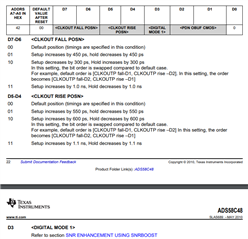

将ADC四通道输出模式设置为输出切换模式,即输出为1.01010101亿和1.0101万01010</s>0.101万

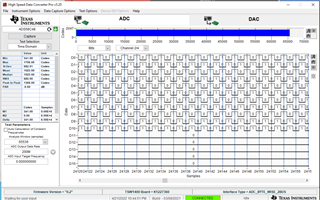

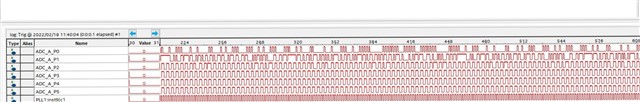

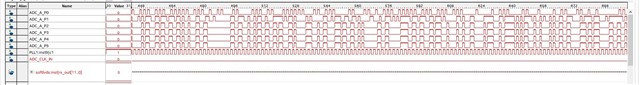

从FPGA端可以看出,在A10,A8,A6和A4上,数据波形符合设置输出模式。 但是,这不是两条LVDS线路A2和A0上的数据模式。 所有四个渠道都存在同样的现象。 配置后读取ADC寄存器值,配置值与读取值一致。

有关详细信息,请参见图。

其他测试:

1.配置输出全零:

配置 输出所有一个:

图中的PLL1是ADC的输入时钟。

2. ADC的输入时钟是FPGA PLL频率加倍直接输出的信号。 频率尝试了20M,40M,50M,80M和100M,幅度是VPP = 2.5V。 时钟输出正确,已通过示波器测量和验证。

3. CM电压为0.95V。

4.此ADC外设设计可在其他项目中正常工作(与此项目不同的是,FPGA已被替换,但针脚定义和配置已验证为正常)。 已测量ADC的电源电压,功耗和配置电阻,没有问题。

5.重新排列多氯联苯后,这种现象是一致的。

出现上述现象的可能原因是什么? 您能否提供一些故障排除建议

此致,

罗艾米