Other Parts Discussed in Thread: ADS7853, ADS7863

各位专家,您好!

你好。 我们有来自CX的此查询(他正在使用免费电子邮件):

ADS7853:14位,1MSPS,但通过SPI读取时,我只接收1kbps的采样速率,您有什么关于瓶颈的建议吗? 我是否需要使用DMA来加快速度?

谢谢你。

此致,

Archie A.(Archie A.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,Ryan:

感谢您的指导。

您指的是SPI时钟吗? CX显著提高了这一速度,但没有变化会产生任何影响。

他指 的是数据表 https://www.ti.com/lit/ds/symlink/ads7853.pdf ,但没有与您提到的"CONVST"或时钟速度相关的寄存器/设置。

您是否可以让我们了解我们可以在何处配置此设置或阅读有关这些设置的更多信息?

谢谢!

此致,

Archie A.(Archie A.

您好,Archie:

我很抱歉-我误读了该帖子的“ADS7863”。

在ADS7853中,有两个信号控制总体ADC吞吐量:SCLK和CSN。 CSN的下一个边缘将启动下一个转换。 在前16个SCLK周期内,转换周期开始,之后将启动MSB和后续数据位。 每个数据输出模式都有一个数据启动边缘表。

转换周期结束后,采集周期即开始。 采集周期的长度由用户控制,持续到下一个CSN下降边缘。

此致,

Ryan

您好,Ryan:

感谢您的更新。 刚收到客户体验反馈:

他 对SPI时钟频率进行了很多实验,但无论他增加多少频率,输出读取都停留在1 kHz左右的采样,即每个新值之间的0.001 - 0.002 秒左右。

您能否确认 这是否与预期绩效有关,或者是否应该能够达到更高的水平? 他们 的交易由完成

CS LOW (CS低)

16位传输+ 32位接收

CS高。

谢谢你。

此致,

Archie A.(Archie A.

您好Ryan:

感谢您的指导。 以下是CX的回应:

"是的,我使用的是32-CLK,单SDO模式(即每个周期最少48个时钟),这是正确的。

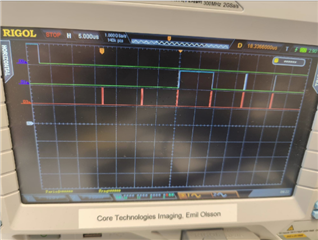

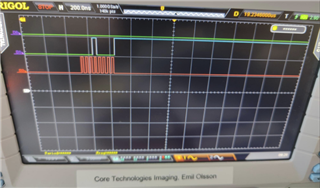

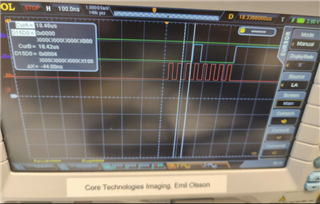

以下是您按顺序(从上面)请求的信号CS,SDO_A,SCLK:

放大SDO_A的第一个上升沿:

因此,我可以看出,ADC在SDO输出32个时钟信号之前,正确地获取了16个时钟信号输入。

这张图片显示两个时钟上升边缘之间大约有44 ns,即如果我正确计算,大约为25MHz。

因此,使用此配置,我(在MCU代码中)正在读取ADC输出,并每秒获得大约1000个完整值。 (1 kHz)。 我想知道,如果我能够实现更高的目标,这是否是预期/合理的表现。"

以获得您的帮助。 谢谢你。

此致,

Archie A.(Archie A.

您好,Archie:

因为Ryan已经不在办公室几天了,所以跳到这里,并将在星期二5/3回来。

看看你的示波器镜头,我不确定第一张图片中的时间/刻度,因为它有点模糊。 是5 us/div吗? 您能澄清吗? 如果您能够明确CS引脚(CS下降边缘到CS下降边缘)的频率,这也会很有帮助。 如果您需要1MSPS,则CS下降边缘到CS下降边缘需要为1/吞吐量或1/(1MHz),即1us。

另一点我想了解的是,为何会有SCLK的间隔。 能否提供恒定SCLK? 由于数据输出取决于SCLK周期的数量,因此使用恒定SCLK时数据输出速度应快得多。

此致,

亚伦·埃斯特拉达