在“线程: LMK0.4828万”中讨论的其它部件

各位同事,您好!

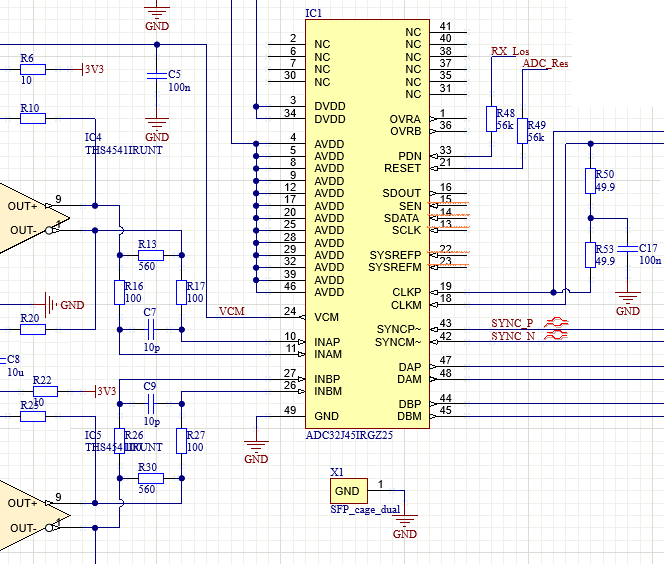

我选择ADC32J45在XFEL (欧洲自由电子X射线直线加速器)的kicker系统中开发测量设备。

第一个结果显示奇怪的噪音,这似乎取决于信号值。 我发布了Vivado Logic分析器的图解,其中显示了接收到的信号(rxdata[15:0],其中两个LSB始终为零)。 转换速度为160ms/s,同步成功,JESD数据没有任何错误,因此问题必然出在模拟端。

噪声峰间电平约为ADC范围的1%,这是14位ADC不可接受的。

在模拟输入端,使用了THS4541IRUNT全差分运算放大器,如评估原理图中所建议。

我的问题:有人知道,这是什么类型的噪音(例如采样故障),原因是什么?

原因可能是ADC损坏?

是否有任何解决方案,例如ADC输入引脚的额外滤波可以防止这种故障?

提前感谢您的回答!

此致

Artur Boebel