您好,Abhishek,

正如您所说的,这是我们可以解决的捕获问题,感谢您的提示。

现在,我们面临着更多的问题,我们可以在ILA中看到正弦波,直到40 MHz输出的30 MHz采样时钟频率不能正常工作。 观察之后,我们尝试通过 使用SPI寄存器(0x25,0x0040)生成斜坡测试模式来检查相同 情况,即使斜坡信号从40 MHz开始不好,我们必须在100 MHz之前完成系统测试,您对此的建议将会非常有帮助。

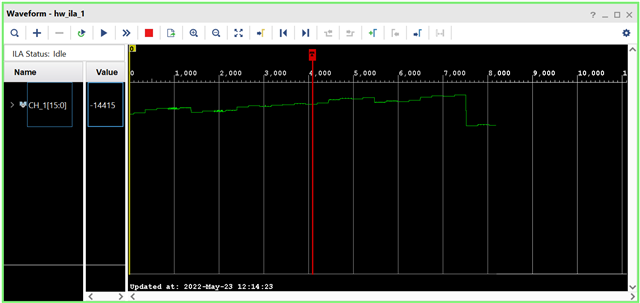

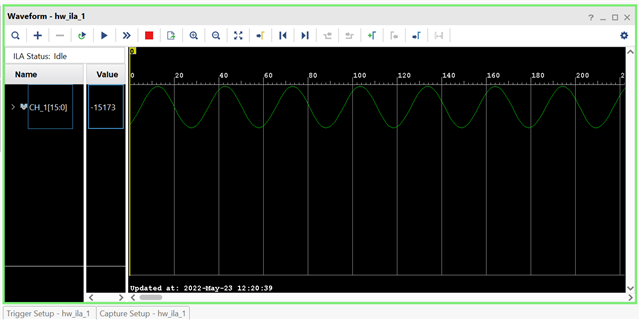

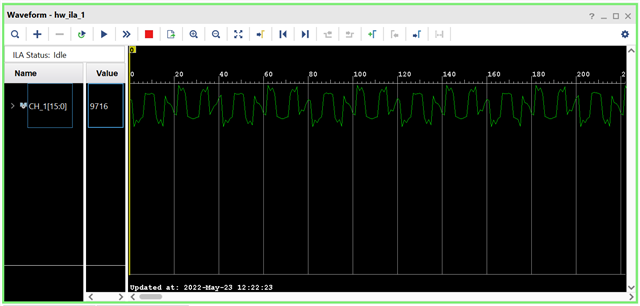

我还附上了国际法协会输出的剪贴,供您参考。

30 MHz采样频率的斜坡

40 MHz采样频率的斜坡

1 MHz输入模拟信号30 MHz采样频率

1 MHz输入模拟信号40 MHz采样频率

我们已使用Xilinx IDDR采集样本