你(们)好

您能否帮助查看 用于 ADC34J44输入阻抗匹配的以下电路? 客户参阅我们的 EVM 设计。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Zhen:

要测试 DVGA 是否超出 ADC 范围、 您需要一种查看 ADC 输出的方法。 可以这样做吗? 您能否可靠地捕获 ADC 数据?

如果可以、您可以查看代码输出、时域输出或 FFT 输出、以查看输入是否使转换器饱和/范围过宽。

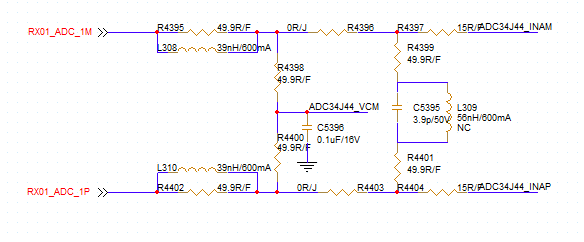

另一种检查方法是使用示波器、例如在 C171/2之后、您可以在 ADC 的模拟输入引脚处进行探头、并以此方式检查信号电平。 每个桥臂只能承受1VDC 左右的+/-500mV 电压。 或0.5V 至1.5V。 如果信号较大、则表示转换器饱和。 随附图片以进行说明。

ADC 的输入满量程为2Vpp、输入直流共模电压为1V。

此致、

Rob