主题中讨论的其他器件:LMK04828、 LMX2594

大家好、

我们客户的一个问题、如下所述:

JMODE1、ILA 观察到的同步信号被拉低、但 xillnx IP 内核 tdata 没有数据输入(K28.5)、当我将 ADC R203寄存器设置为0 (JSYNC_N = 0)时、IP 内核仍然没有 K28.5输入。

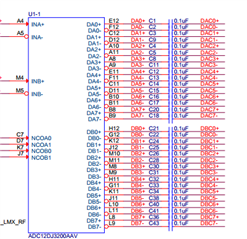

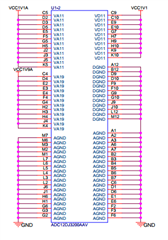

客户使用自己的设计板、FPGA 为420T、REFCLK 和 FPGA 的参考时钟由 LMK04828生成、LMK 连接 LMX2594以输出 ADC 器件时钟和参考时钟。 示波器可以观察生成的时钟信号。 这是 ILA 捕获的信号

您可以提出任何故障排除建议吗?

寄存器配置:

分配 cfg_mem[0]={15'h0000, 8'hB0};//重置

分配 cfg_mem[1]={15'h0200、8'00};//对 JESD_EN=0进行编程以停止 JESD204B 状态机并允许更改设置。

分配 cfg_mem[2]={15'h0061、8'00};//编程 CAL_EN=0以停止校准状态机并允许更改设置

分配 cfg_mem[3]={15'h0201、8'h01};//编程所需的 JMODE。 JMODE=1

分配 cfg_mem[4]={15'h0202,8'h1f};//编程所需的 KM1值。 Km1 = K-1

分配 cfg_mem[5]={15'h0030、8'hFF};//1000mVpp

分配 cfg_mem[6]={15'h0031、8'hFF};

分配 cfg_mem[7]={15'h0032、8'hFF};//1000mVpp

分配 cfg_mem[8]={15'h0033、8'hFF};

根据需要分配 cfg_mem[9]={15'h0204,8'h02};//对 SYNC_SEL 进行编程。 选择 SYNCSE 或时间戳差分输入和 SCR。//SYNC_SEL =1 TMSTP

分配 cfg_mem[10]={15'h0203,8'00};//

分配 cfg_mem[11]={15'h0205,8'00};///正常0:测试模式 d

分配 cfg_mem[12]={15'h0213、8'h07};//启用超范围,将超范围保持设置为最大周期8*2^7 = 1024个样本8*2^7 = 1024

分配 cfg_mem[13]={15'h00488'h03};//将串行器预加重设置为3

//assign cfg_mem[14]={15'h0060、8'h01};//输入多路复用器控制寄存器01:单输入 A;02单输入 B

分配 cfg_mem[14]={15'h0029、8'h30};

分配 cfg_mem[15]={15'h0029、8'h70};

分配 cfg_mem[16]={15'h0029、8'h73};

分配 cfg_mem[17]={15'h0061、8'h01};//编程 CAL_EN=1以启用校准状态机。

分配 cfg_mem[18]={15'h0200、8'h01};//对 JESD_EN=1进行编程以重新启动 JESD204B 状态机并允许链接重新启动

将 cfg_mem[19]={15'h006C、8'00};//将 CAL_SOFT_TRIG 设置为低电平以重置校准状态机

将 cfg_mem[20]={15'h006C、8'h01};//将 CAL_SOFT_TRIG 设置为高电平以启用校准

分配 cfg_mem[21]={15'h02C0、8'00};

分配 cfg_mem[22]={15'h02C2,8'00};

分配 cfg_mem[23]={15'h02C1、8'h1f}

此致、

罗美