主题中讨论的其他器件:TMS320F28388D、

您好!

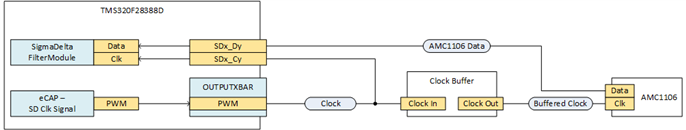

我正在努力处理 AMC1106M05 Δ-Σ 调制器的信号时序以及 TMS320F28388D。 我的原则是:

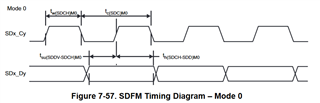

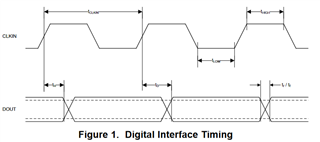

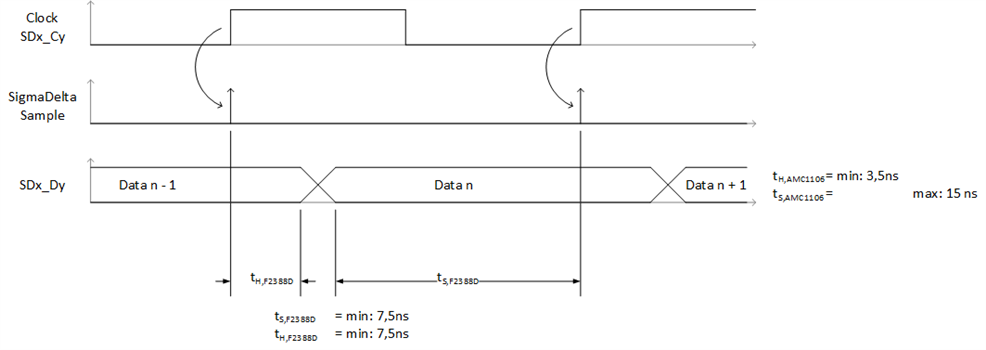

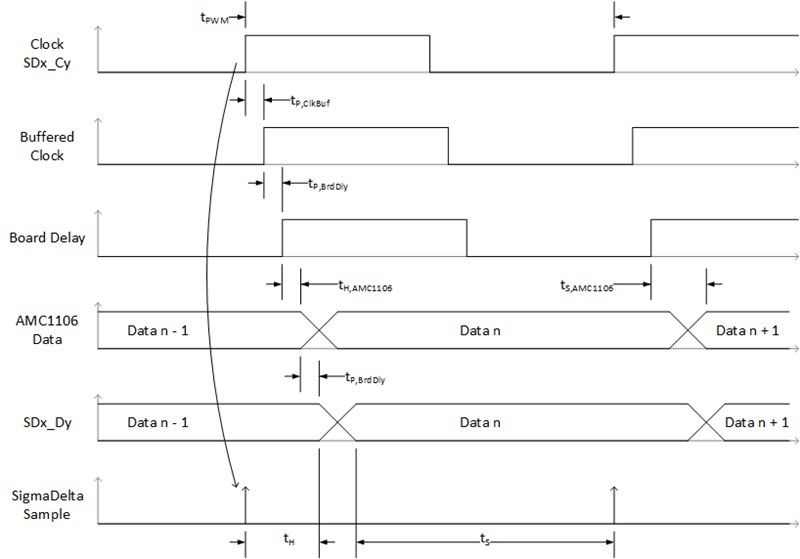

时序图如下所示:

为了评估保持时间的要求已满、我从 AMC1106和 TMS320F28388D 的数据表中获取以下值:

TH、AMC1105 = 3.5ns (时钟输入上升沿之后数据输出的保持时间)

TS、TMS320 = 1*PLLRAW + 5ns = 10ns (所需的保持时间、sdX_Dy 在 SDX_Cy 变为高电平后等待)

信号链的保持时间可通过以下公式计算:

TH = TP、ClkBuf + TP、BrdDly + TH、AMC1105 > TS、TMS320

如果我假设时钟缓冲器相当快(很难找到慢速时钟缓冲器),或者甚至不在信号链中,那么延迟为 TP,ClkBuf = 0ns ... 1ns PCB 信号传输引起的延迟进一步在 TP、BrdDly = 1ns 范围内... 3ns 该公式将导致:

th = 0ns + 1ns+ 3、5ns = 4、5ns、 不幸的是、这低于10ns。

换言之、这意味着 、在 TMS320F28388D 对数据进行采样的时刻 、无法确保 AMC1106 保持数据输出足够稳定。

我的实施是否正确? 我在想什么地方时出错了吗?

此致、

Michael Kettler