您好!

我们在其中一款产品中使用了6 ADS1220。 它们都在连续转换模式下进行完全相同的配置、通过同一 SPI 总线进行通信、并由相同的3MHz 信号(CLK 引脚)计时。 "START"命令通过 SPI 发送、同时激活所有6个 CS 引脚、然后轮询单个 DRDY 引脚以触发从 STM32收集所有6个 ADC 的数据。

我们通常没有任何问题、但一些样本会在一段时间内连续应答0xFFFFFFF。

发生这种情况时、大多数 ADC 工作正常、但一个(很少有)仅在读取连续数据时应答0xFFFFFFF、并在读取配置寄存器时应答0xFFFFFFFF。 这种情况可能会持续很长时间、或在断电后消失。 它可能会再次出现在同一个 ADC 或另一个 ADC 上。 有些系统通常出现故障、而其他系统则出现一次、因为大多数系统从未出现过故障(我没有非常精确的估算、但我会说200多种产品的样本数小于10个)。

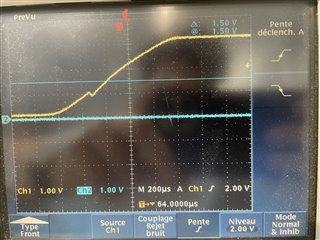

我们设法实时测量 SPI 信号、MISO 线路在 CS 激活时有效地驱动为高电平。

我们在一侧发现了实施错误:外部3MHz 时钟的占空比为25%,而不是40-60%,但由于我们缺少可靠的故障器件,我们无法轻易地确认这一原因。

此错误能解释我们的问题吗? 或者、此问题是否与已知问题或常见滥用有关?

此芯片是否有勘误表?

我知道这一描述并不完整,但解释整个系统和调查将会很长时间;如果需要,请随时向我询问更多详细信息。

谢谢、

Etienne。