Other Parts Discussed in Thread: ADS8864

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS8864 大家好、团队、

您能否澄清以下几点:

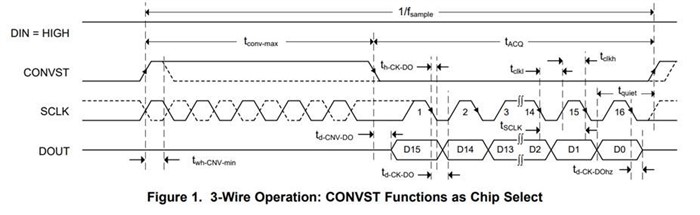

- Tsample 由 tconv_max 和 Tacq 定义。 Tconv_max 为1300ns、因此 Tacq (Tacq 同时是最小值)的时间为1200ns、达到2500ns tsample (400kSps)。

- Tacq = 1200ns = TD_cnv_DO + 16 tsclk +裕度-> Tacq = 12、3ns + 16x62,5ns +裕度@ 16MHz SPI SCLK

- ->这意味着、如果 SPI SCLK 为16MHz、如果将 Tacq 延长至1200ns、400kSps 的时序限制是可以达到的

- 是这样吗?

- Tacq = 1200ns = TD_cnv_DO + 16 tsclk +裕度-> Tacq = 12、3ns + 16x62,5ns +裕度@ 16MHz SPI SCLK

- 只要 DIN 和 CONVST 是高电平、SPI 总线上的其他 IC 就可以使用 SCLK 和 DOUT 而不会发生任何冲突、对吧? 因此,ADS8864不会对任何 SCLK 做出反应,并且在此期间将 DOUT 保持高阻抗? 因此、当 DIN 和 CONVST 为高电平时、我可以与其他 IC 通信。

- DOUT 在第16个 SCLK→后变为高阻抗意味着 CONVST 可以保持低电平直到下一个转换周期、而其他 IC 可以同时使用 SCLK 和 DOUT 而不会发生任何冲突?

谢谢、

日落