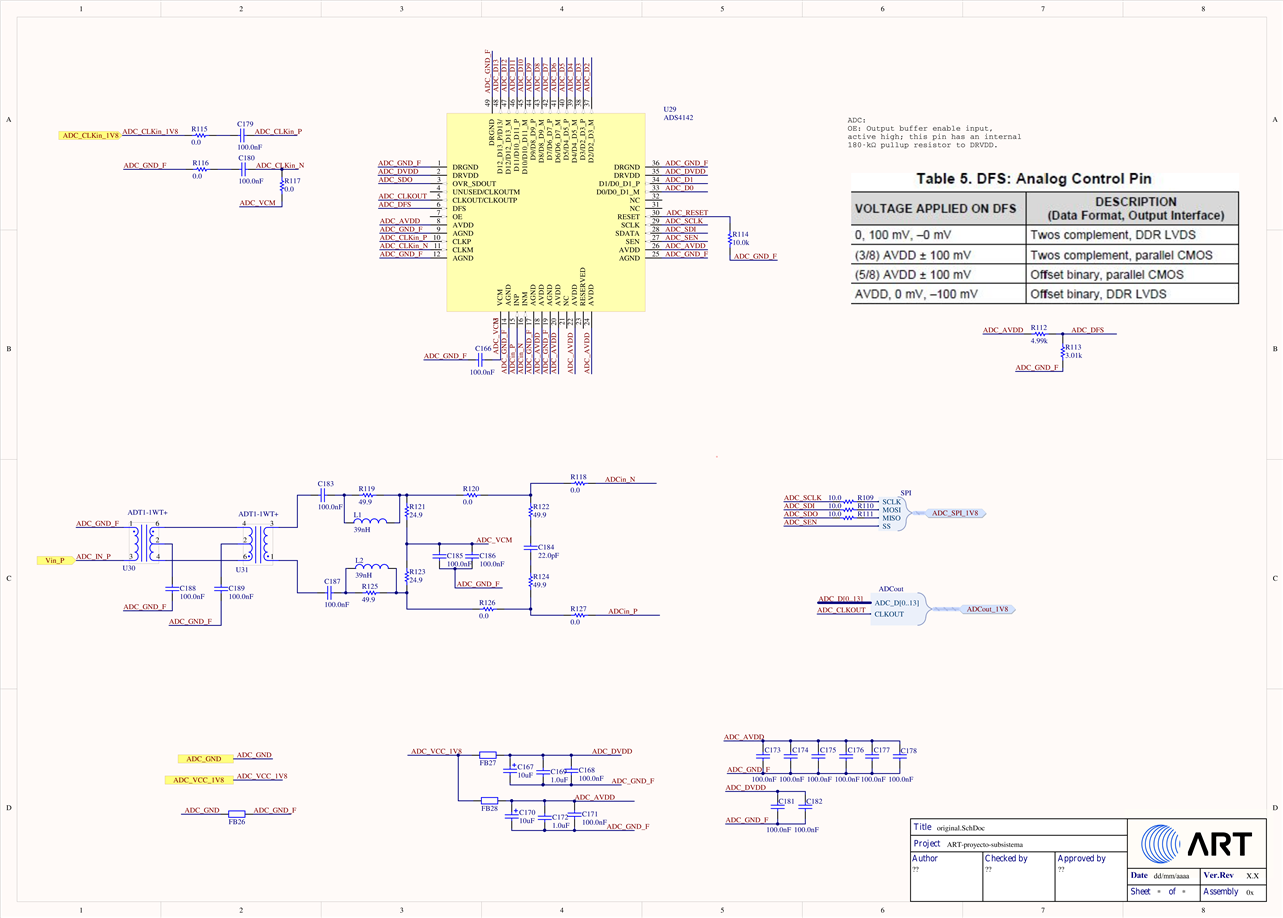

Other Parts Discussed in Thread: ADS4142

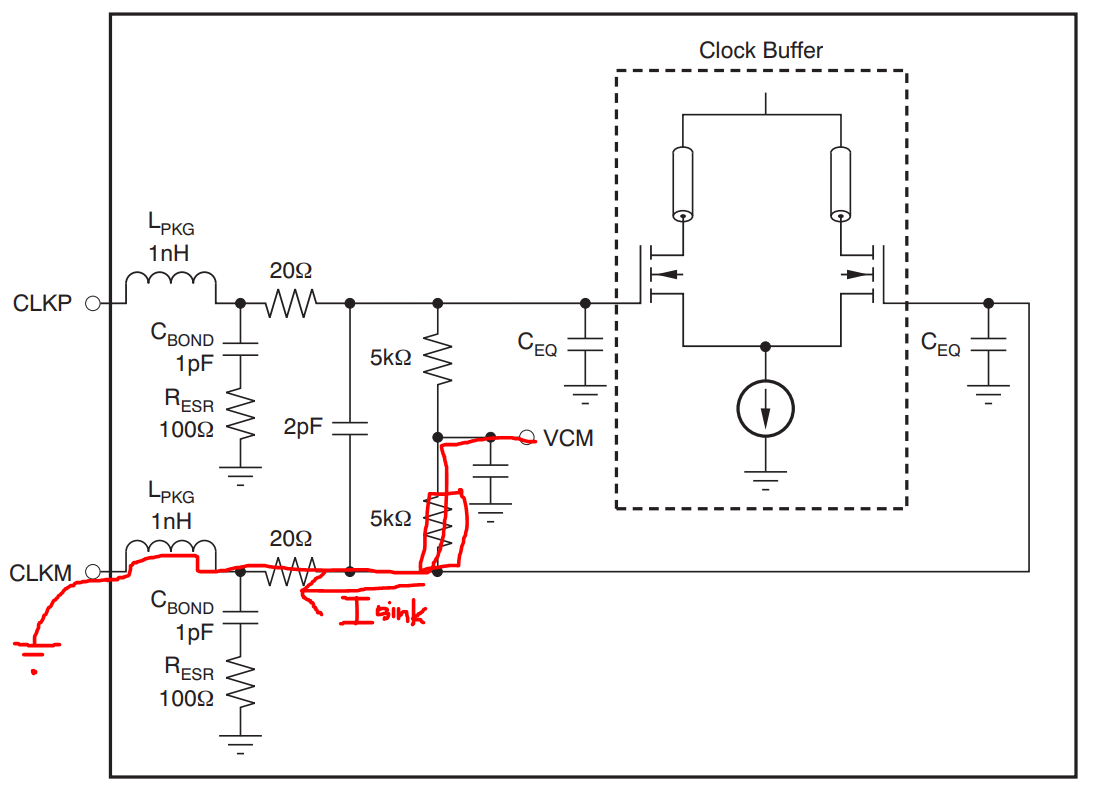

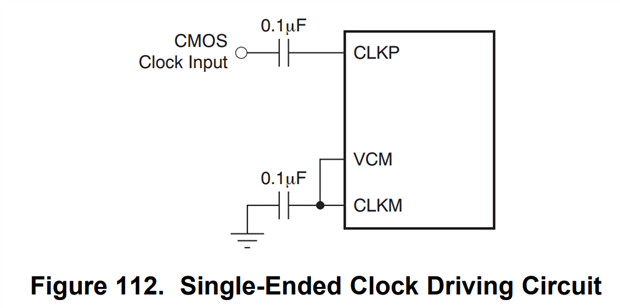

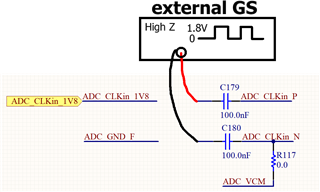

大家好、我正在尝试了解 Clk 输入周围的电路。 我看到它允许 CLKN 和 CLKP 之间的差分信号、而差分正弦波时钟的电路仅将输入到这些引脚中。 但是、CMOS 示例不像我预期的那样将 CLKN 连接到 GND、而是将该引脚连接回 Vocm 信号。

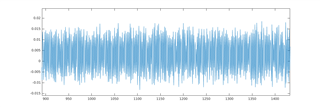

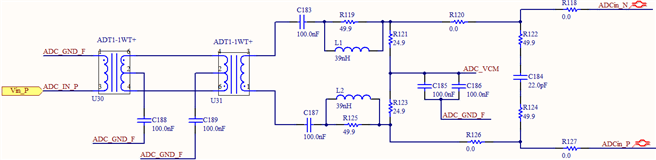

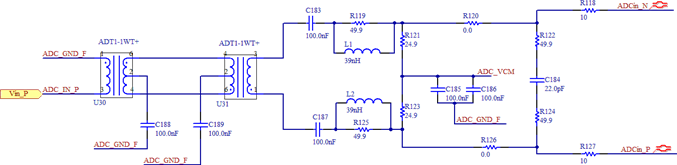

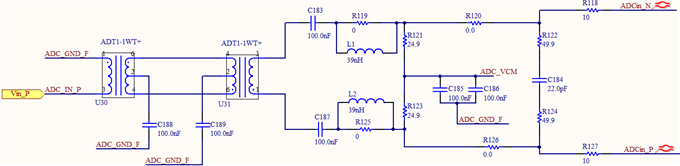

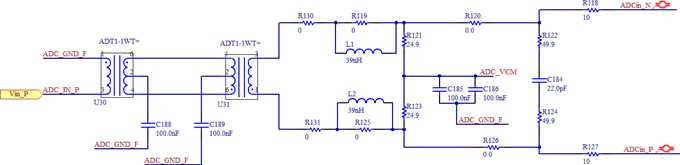

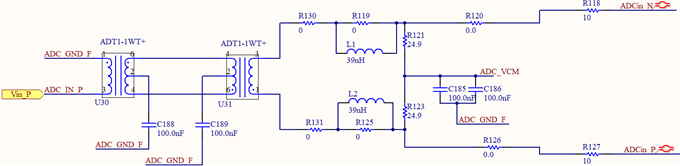

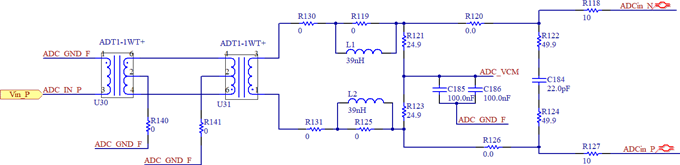

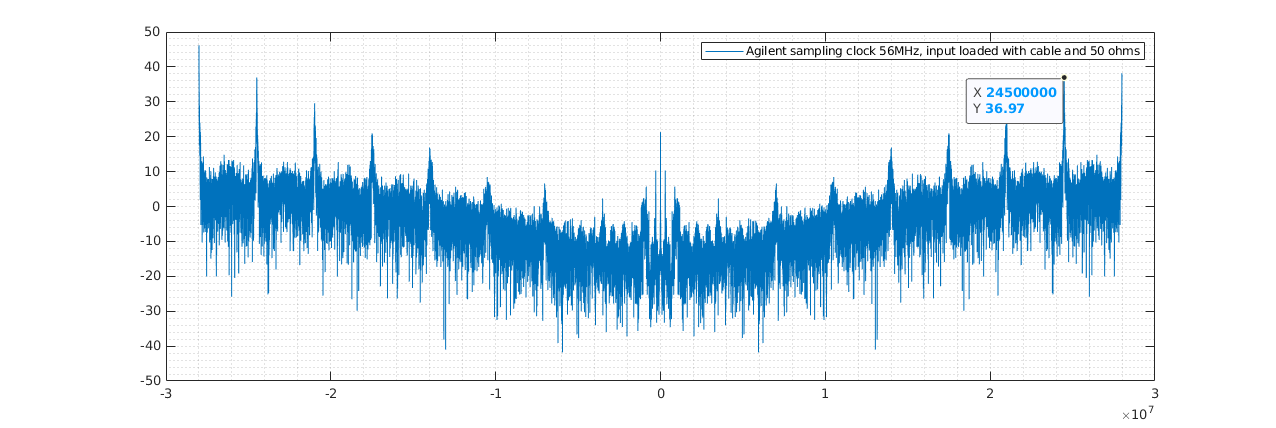

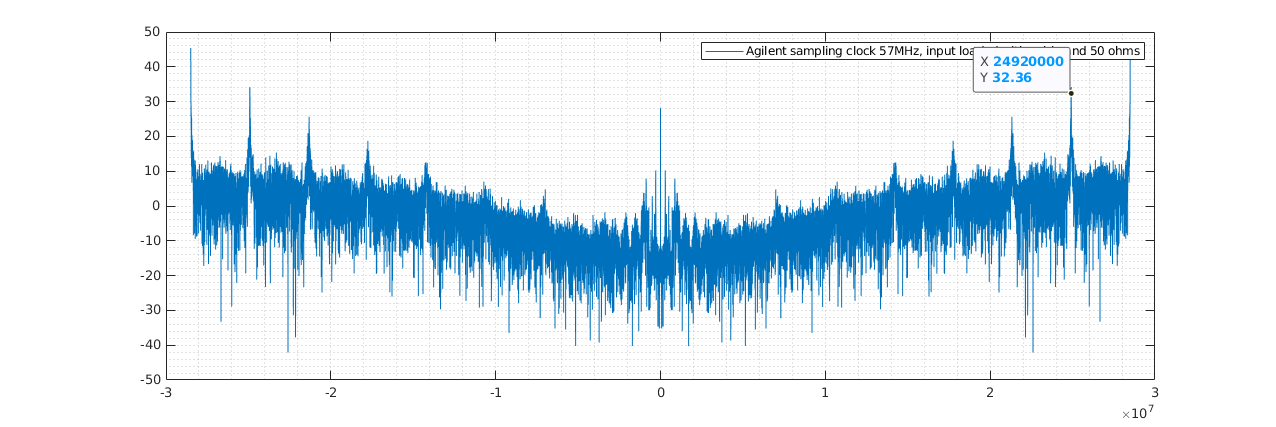

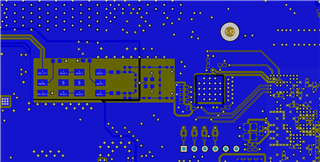

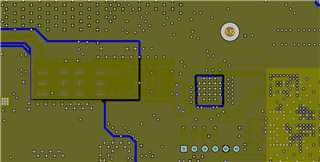

我已经使用这个作为基准来实现我自己的电路板、以及基于两个变压器的输入电路。 使用示波器进行测量时、我看到 Vin_p 和 Vin_n 处出现非常高的噪声、看起来时钟相位噪声正通过 Vocm 信号传输到输入端。

我不确定我的噪声是否来自时钟、但我仍然不完全了解时钟输入电路、因此我希望对此有一些了解。 我是否可以将1.8V CMOS 时钟直接连接到 CLKP、将 CLKN 直接连接到 GND?