主题中讨论的其他器件: LMK04828

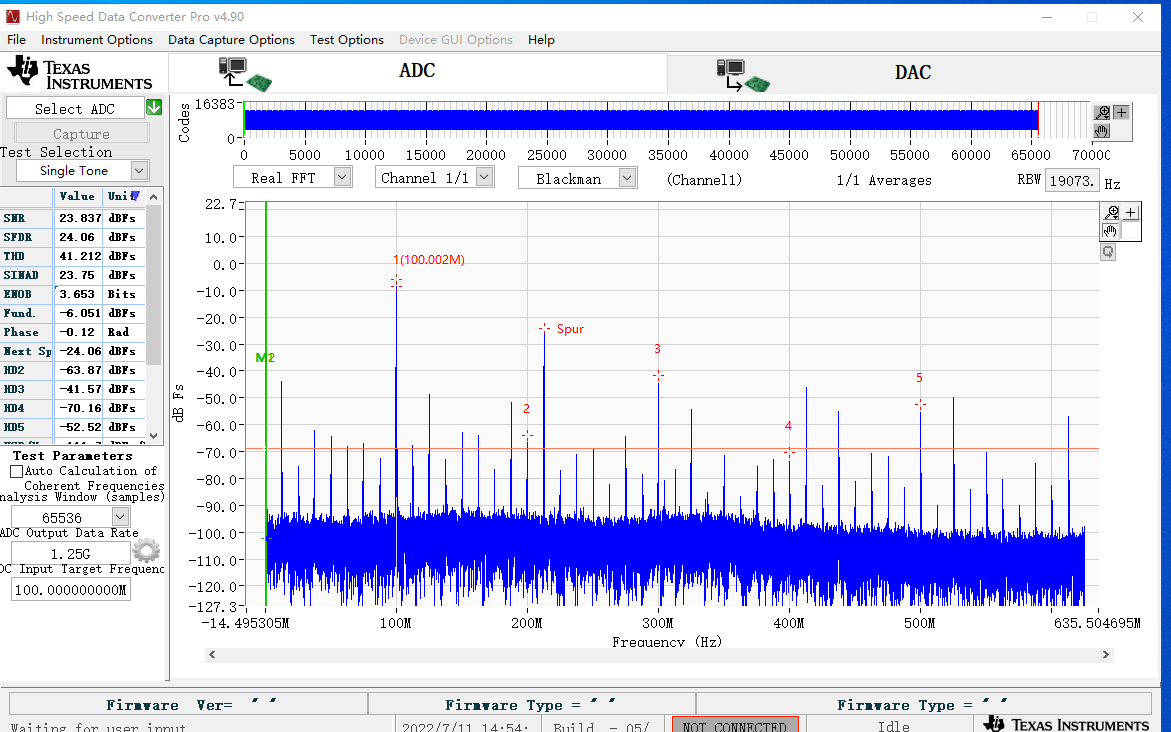

这使用2x 内插生成 频谱:

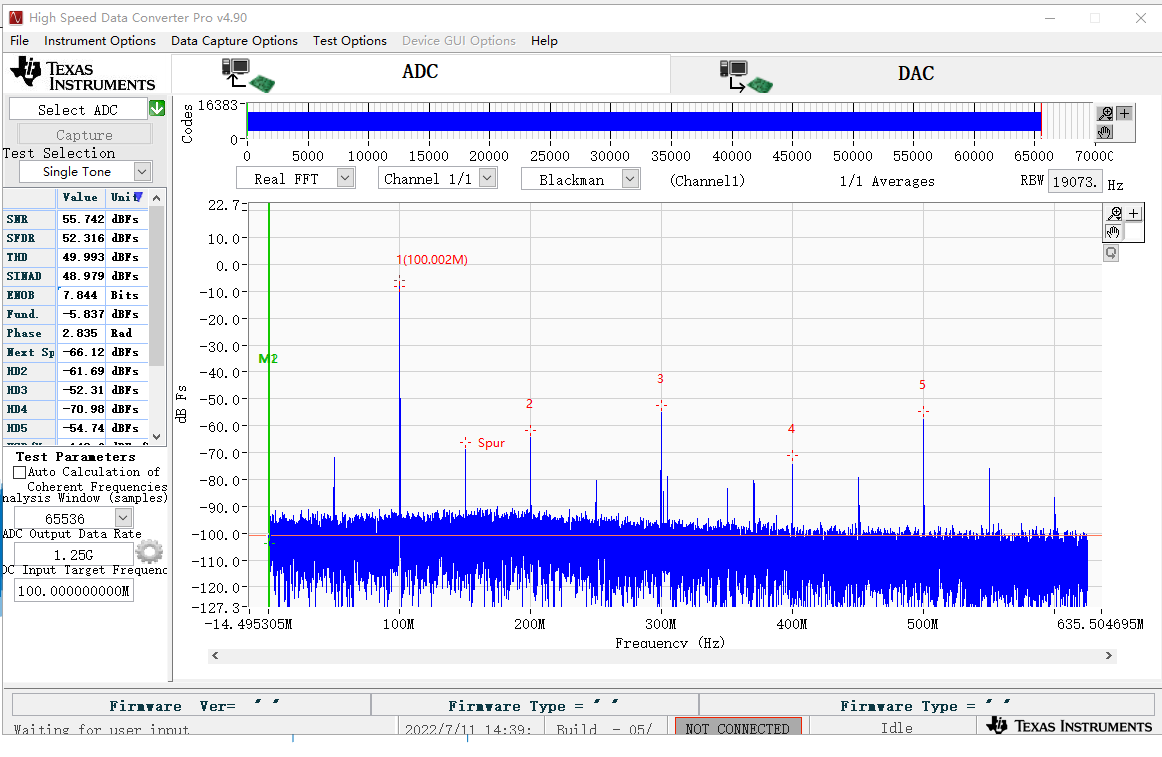

这使用1x 内插生成 频谱:

为什么它们如此不同? 如何设置寄存器、以便频谱可以正常进行2倍插值? 如何使用 fir0过滤器?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

陈

使用您的设置并使用图形发生器卡进行测试时、我没有看到此问题。 随附的是我使用的测试提示音。 这是一个100MHz 音调、数据速率为1250Msps、65、536个样本。

此致、

Jim

陈

我的设置中的 JESDCLK_DIV = 4、等于(插值* L)/M。如果您的系统使用的是 jesdclk_div = 2、我认为您的输入时钟可能会关闭2倍。

已附加配置文件。

此致、

Jim

e2e.ti.com/.../DAC39J82_5F00_4211_5F00_2500_5F00_Fs_5F00_2x_5F00_Int.cfg