模式:VLP

采样率:64KSPS、数据接口采用 SPI、配置为三字节(24位)数据上传(即 禁用状态字)、

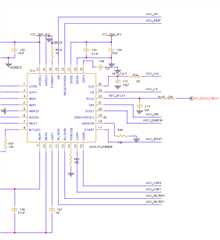

以菊花链形式显示的电路如图1、2和3所示:

现象1:

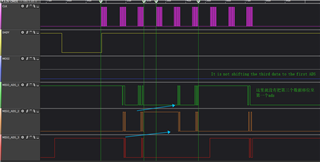

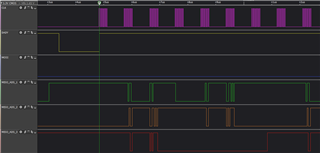

将收集三个通道的数据、发现最后一个 ADS 的数据不会通过移位寄存器移动到第一个 ADS。此外、在读取数据时、 DRDY 引脚在 SCLK 的第一个周期中有时不会上拉。图6的 DRDY 正常、但数据仍然错误(这是第二个周期的 DRDY、

后续周期 DRDY 有时正常、有时不正常)。

现象2:第三个通道的 ADS 数据已成功移至第二个 ADS、但未移至第一个 ADS 和输出、如图7所示。