大家好、

客户遇到 ADC SPI 通信问题。 请参阅以下信息:

我可以«数据、但 ADC Δ Σ 不能 »转换数据时、会不时地读取该数据。

我遵循数据表并在 FPGA 中编写 SPI 代码、以从 ADC 获取数据。

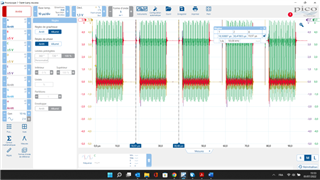

因此、我同时在 CONSTA、B、C 和 D 上发送转换请求、然后等待 BUSY 下降、并在 FS 上放置0以读取 SDO_A、B、C 和 D 上的数据。只有当 FPGA 中的数据为红色时、才会生成 SCLK。

SCLK = 2、75MHz ->时钟用于同步 SDOA、B、C 、D 上的数据

CONV Clk = 50kHz ->频率以启动转换序列

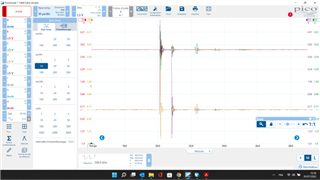

绿色轨迹: SCLK

红色曲线 :fs

蓝色曲线 :CONVST

棕色轨迹: 忙

前两张图片显示了正确的行为、我可以正确读取数据

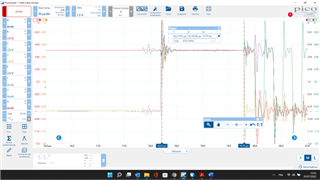

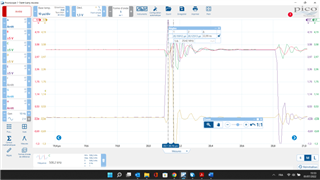

下图显示了转换失败时的信号。 BUSY 会立即接收几 ns、显然转换失败、因为我无法想象转换如此快速。 µs (成功转换时)大约需要2 μ s 进行转换。

我不认为 ADC 有问题、可能我缺少了一些东西。 如果有任何建议、我们将不胜感激。

希望能帮客户。

谢谢!

此致、

Marvin