主题中讨论的其他器件: DAC38J84

您好!

我使用的是 DAC38J82 DAC IC。

对于 JESD 接口、培训材料《德州仪器 JESD204B 系列物理层 PHY》中提到必须将交流耦合电容器放置在发送器侧。

但在 DAC EVM-DAC38J84EVM 中、它放置在接收器侧附近。

如果布线长度超过4英寸、则应将交流耦合电容器放置在何处?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Sarojini、

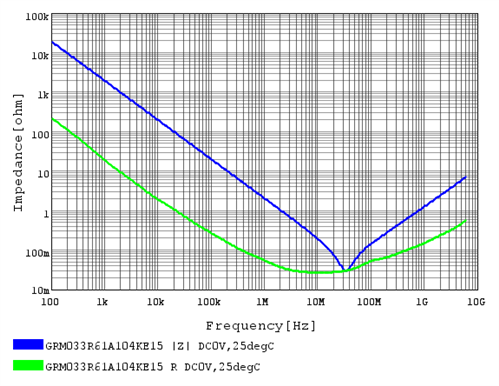

通常、建议将这些电容器放置在发送器侧附近、以最大程度地减少传输线上累积的反射量、 但是、如果在相关频率下电容器阻抗远低于线路阻抗、则放置在接收器侧也会起作用(如 EVM 上所示)。 线路阻抗为50Ω Ω。 EVM 上的交流电容为 Murata GRM033R61A104KE15D、如果您查看该电容器的频率阻抗特性、您会发现高达8GHz 左右、阻抗为5Ω Ω 或更低。 我们可以假设超过10GHz 的阻抗将处于几个欧姆级别、不像8GHz 及以下理想值、但仍然适用。

您希望避免将电容器放置在总通道距离的中间位置(如果我们的电容器最靠近 EVM 上的 FMC 连接器、则会出现这种情况)、因为这样可以在两侧产生驻波和反射。 我建议将这些放置在距离您的 FPGA 最近的位置。 使用涵盖您计划在中操作 DAC38J84的串行器/解串器范围的低阻抗0201电容器、以最大程度地减小放置对信号完整性的影响。

此致、Chase