主题中讨论的其他器件:ADS1282

尊敬的 Christopher:

为了使基准电压尽可能保持稳定和清洁、 我将 AVDD 引脚连接到由线性稳压器供电的专用5V_SENS 电源、并将 VREFP 引脚连接到由具有外部 NPN 晶体管的 AD584基准发生器生成的5V 基准电压。

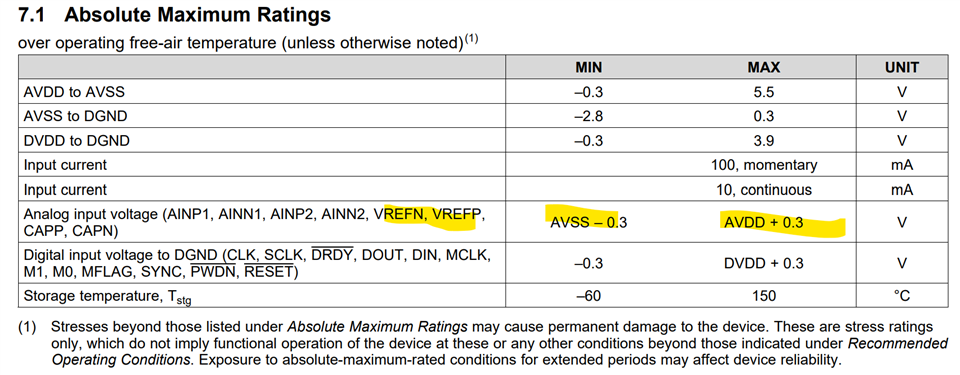

我的5V_SENSOR 电源由于预期的故障而关闭、而 VREFP 保持开启。

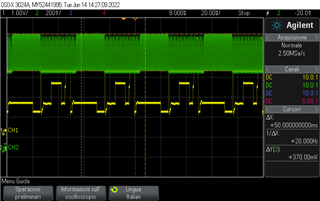

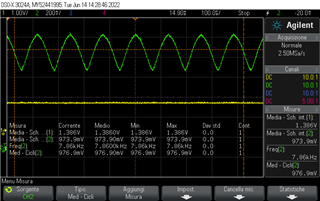

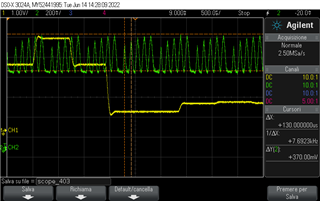

ADC 开始在 AVDD 上灌入40mA 电流、并在选择 PG = 2时提供双倍值的采集。 ADC 对所有命令进行了完美解释和实现、顺便说一下、我连续写入 CONFIG1寄存器以保持 PG = 1选择。 此外、我检查了 PGA 的输出、它提供了1x 增益选择的证据。

我认为 ADC 已损坏并将其从 PCB 上移除。

我的问题是:

在 AVDD 不存在时是否存在 VREFP 是 ADC 故障的根本原因?

其他信息:ADC、由于缺少许多传感器、因此还会在50ms 周期(周期的1/3)内由12V 输入供电、持续时间约为16ms、在 AINP 引脚上吸收约11、5mA 电流-(12V-0.6V)/1k Ω-、 这大于10mA 连续输入电流限制、但远小于临时100mA 输入电流限制。

提前感谢您、

此致、

Daniele Lippi