主题中讨论的其他器件:DAC39J84

大家好、我下载了 TI-JESD204B IP、并使用适用于 VC707 FPGA 板和 DAC39j84的 zc706_8b10b 参考设计。 我使用 LMFS=8411、HD=1。 以下是在实施过程中使我感到有问题的几个方面:

参考设计没有 sysref 输入、所以如果我们只连接一个 DAC39j84板、我们是否需要 sysref 输入? 这是否意味着、如果我们不使用多 DAC 板、我们不需要 sysref 信号? 或者我们需要在 实际设计中添加 sysref?

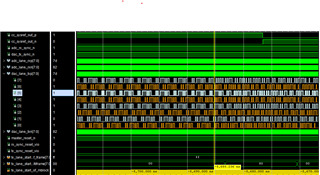

2.我的设计不起作用、当我检查 ILA 时、我发现 TX_LAIN_START_FRAME 为1、但 TX_LAIN_START_ON_MULTIFRAME 为0。 这是否意味着我的设计中有问题? 我对该部件有点困惑。

3. 如果 cfg_TX_ILAS_TEST_MODE=0、我们将不会有用于 TX 的 ILAS 过程、对吧? 如果为1、ILAS 系列是什么? 它是从 K28.0到 K28.3的4字节吗?

4.在设置期间,我在 clkout0和 sys_clk_sys_pll1之间徘徊,这是否会对设计造成问题?

感谢 Advance 的帮助。

最棒的

Shuyi