主题中讨论的其他器件: THS4551

我正在使用 ADC3663测试原型板。 AD 差分驱动器原理图遵循随附的数据表和 ADC3663 EVM 板的建议。 输入是单端2MHz 纯正弦 信号、但 THS4551的输出和 ADC3663的输入具有相同采样频率(50MHz)的大尖峰。

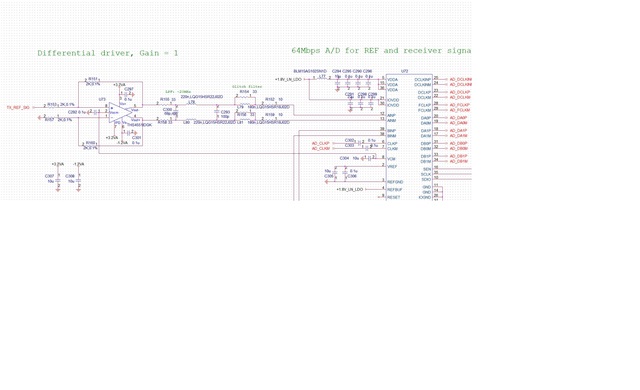

干净的2MHz 单端正弦信号输入

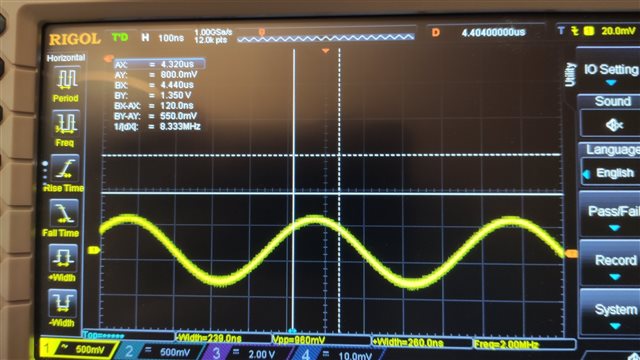

THS4551上的输出和 ADC3663的输入

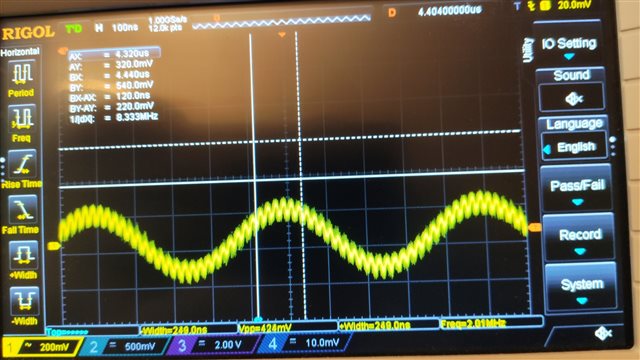

在我阅读了几篇文章(例如、 由 Walt Kester 提供的高速采样 ADC)、由于 ADC3663是一款非缓冲 ADC、这些尖峰似乎是 ADC 在采样过程中回退的结果。 在我移除 R152和 R159后、THS4551的输出端的尖峰消失、这证明它确实是 ADC3663回踢的结果。 在采样时钟的上升沿、ADC 内部开关将模式从跟踪更改为保持、这会在几 ns 内将~1mA 电流引入差分驱动器的输出。 这会导致100mV 尖峰(假设总阻抗为100 Ω)。 然后、在采样时钟的下降沿、ADC 内部开关将模式从保持更改为跟踪、由于 ADC 电容器充电、这会在几 ns 内引入5mA 电流、从而再次产生尖峰。 因此、它需要差分驱动器能够在下一个上升采样边沿之前对 ADC 电容器快速充电。 因此差分驱动器的闭环增益需要高于采样率。 但是、该要求与抗混叠 LPF 相冲突、因为 LPF 至少需要小于采样率的一半? 另一个问题来自示波器显示屏、建议的驱动器原理图和差分驱动器似乎不够快、无法驱动 ADC 的输入以稳定至实际信号电平(采用2MHz 正弦波、也不存在直流电平)。

输入为0V 时出现尖峰;因此、驱动器在采样期间似乎无法完全稳定至实际信号电平

我的理解是否正确以及是否有任何解决问题的建议? 谢谢。