主题中讨论的其他器件:AM2434、 DAC8568

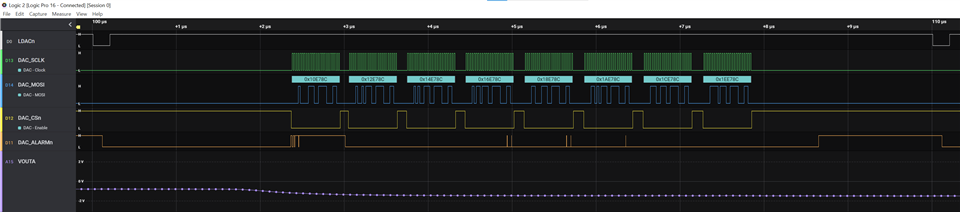

大家好、我正在使用 AM2434对 DAC81416进行编程 、其中 LDAC 由外部时钟独立触发。 触发 LDAC 后、我将立即加载下一组 DAC 值、以备后续 LDAC 使用。

问题1:

LDAC 输入看起来是电平敏感的、而不是边沿触发的(例如、不像 DAC8568)。 我的意思是、如果 LDAC 保持低电平并且我写入 DAC 输出寄存器、则输出立即发生变化、而不是在下一个 LDAC 下降沿发生变化。 我的理解是否正确? 如果是、请在手册中进行澄清。

这 种行为不是世界的尽头、但它确实意味着需要额外的工作来管理 LDAC 占空比。

问题2:

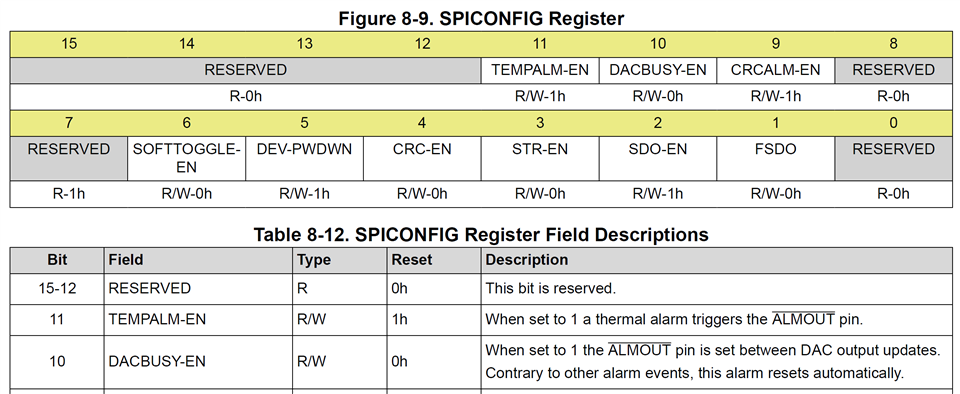

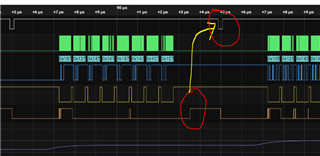

我 在这里阅读了讨论 LDAC 到 CS 的时序的主题(如中需要~2.4us)。 我发现我可以将 BUSY 位映射到警报引脚并使用 上升沿(即 DAC 不忙) 来控制 下一个 DAC 值的写入。 这是可接受的方法吗?

问题3:

我是否需要在 同步模式下写入 DAC 输出寄存器之间添加延迟? 此时、自然延迟为~126ns。 它似乎可靠地工作、但我应该使用忙位吗? 我担心 的是、我将超出更新时间预算。

顺便提一下、LDAC 的定序在手册中并不清楚-时序图将会非常有用。

谢谢、

Steve

附注:供参考的是、我已附上显示序列的当前时序图(忽略警报信号上的毛刺脉冲-这是一个测试物理极限的工作台鼠巢测试)。 是否有更好的方法对其进行排序?