您好!

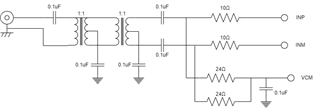

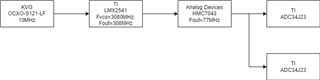

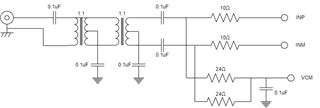

我在我的设计中使用 ADC34J23。 目标频率为327MHz、因此我在数据表(图206)中采用了高输入频率(Fin > 230MHz)的电路设计。

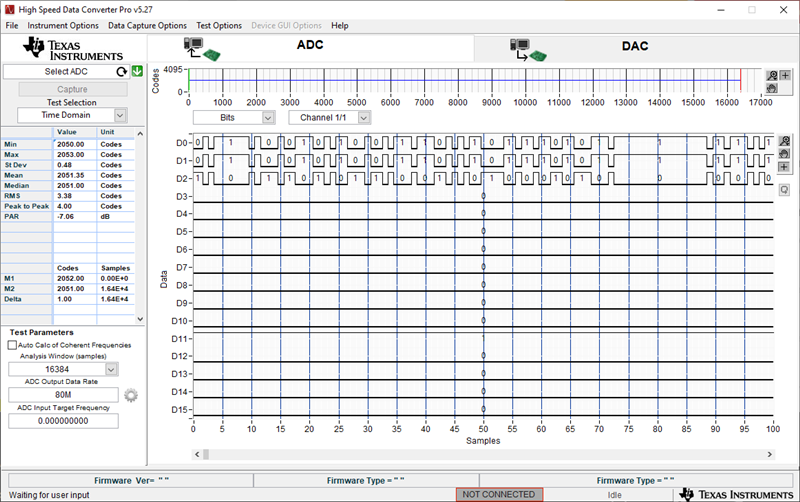

然而、实际乘积的 ENOB 非常糟糕、我发现输入信号在 IC 输入引脚( 图206中的10Ω Ω 电阻器)之前的电阻器上使用差分示波器获得了如此多的噪声。

我一直在研究原因、并意识到数据表中的电路设计 与 评估板略有不同。

25Ω 高输入频率、在10Ω Ω 电阻器和评估板上的 IC 输入引脚之间还有另一个部件(Ω 电阻器、10pF 电容器、56nH 电感器)。

它们为什么不同? 这种差异是否会导致输入信号产生噪声?