Other Parts Discussed in Thread: ADC3663, ADC3663EVM

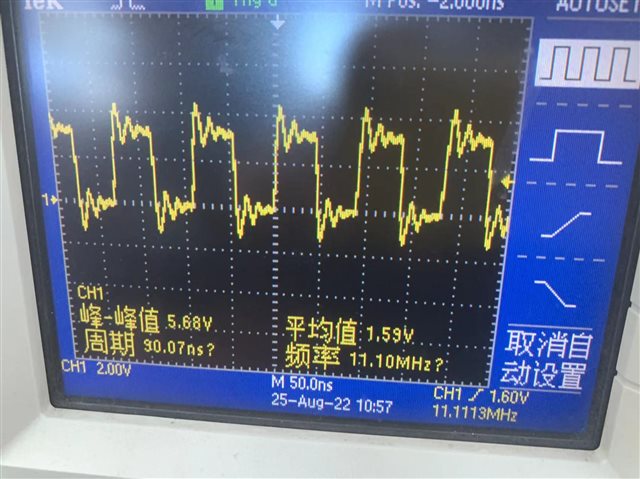

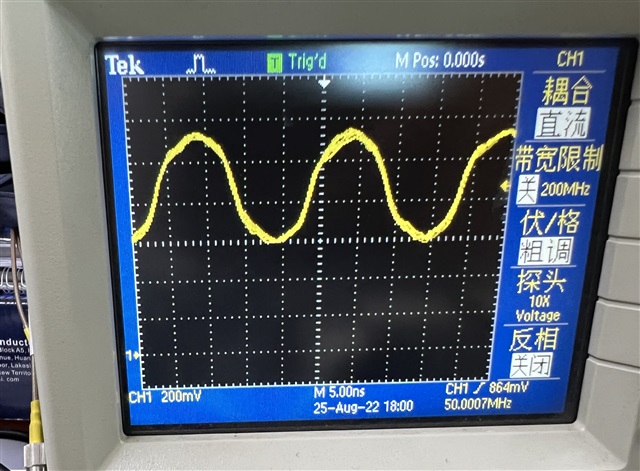

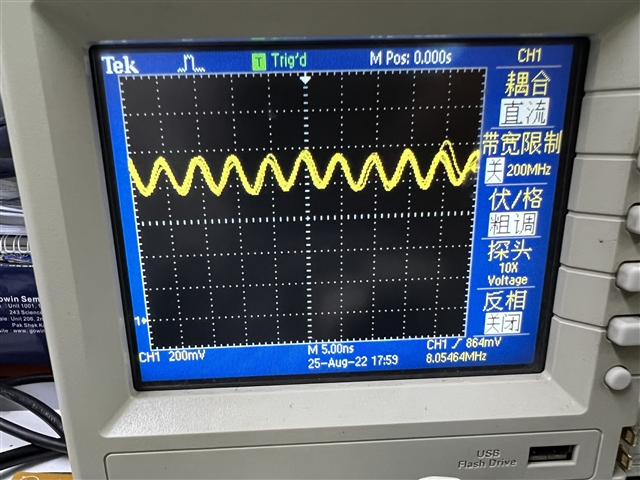

大家好、我使用的是 ADC3663、当采样频率为50MHz 时、设置如下:2Wire、16位和 DDC 设置为 BYPASS、CLK 输入时钟为50MHz、DCLK 输入时钟为200MHz。 不过、AD 的 FCLK 时钟输出不是25MHz、其占空比不是50%。 然后、只要 DDC 使用 BYPASS、就会执行其他采样率测试、结果发现 AD 的 FCLK 输出不是占空比为50%的时钟信号、而 DDC 的提取率设置为2或其他正常值。 我是否可以问、什么寄存器设置错误可能会导致这种现象?