请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC128S102 是 Verilog 模型、时序可用于数字仿真。

ADC128S102上的 SPI 是否也遵循 SPI-TI 标准。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

是 Verilog 模型、时序可用于数字仿真。

ADC128S102上的 SPI 是否也遵循 SPI-TI 标准。

您好 Ramesh、

首先、欢迎访问 TI E2E 社区。

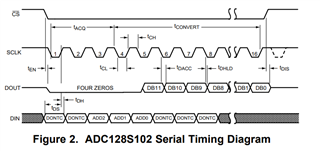

遗憾的是、没有可用的 Verilog 或 VHDL 模型、只有 IBIS 和 SPICE 模型。 SPI 接口遵循业界通用模式3、CPOL=1、CPHA=1。 数据在 SCLK 下降沿被启动并在 SCLK 上升沿被捕捉。 时序详细信息显示在数据表的图2中。

此致、

Keith Nicholas

精密 ADC 应用