大家好、

数据表已从修订版本 C 更改为 D

我知道建议的电路有两个变化:

从 CMP 到 GND 的额外100pF 电容器

从模拟电源到器件 AVDD 的附加10 Ω 串联电阻

如果还有其他更改(附加)点、您能告诉我们这一点吗?

目前,我们的电路没有100pF 和10欧姆电阻。

请告诉我们您的疑虑吗?

此致、

隐藏

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

数据表已从修订版本 C 更改为 D

我知道建议的电路有两个变化:

从 CMP 到 GND 的额外100pF 电容器

从模拟电源到器件 AVDD 的附加10 Ω 串联电阻

如果还有其他更改(附加)点、您能告诉我们这一点吗?

目前,我们的电路没有100pF 和10欧姆电阻。

请告诉我们您的疑虑吗?

此致、

隐藏

hide-san、

仅当从 CMP 到 VOUT 使用较大的电容器时、才需要100pF 电容器。 对于470pF 或更低的 CMP 电容值、不需要从 CMP 到 GND 的额外100pF 电容。 在某些情况下、具有较大 CMP 电容器的电快速瞬变可能会通过 CMP 引脚将 VOUT 的电荷耦合到输出放大器的内部节点。 这可能会损坏器件。

添加了串联电阻、因为电源的快速斜升(~1nV/秒)可能会损坏器件。 当器件的供电方式与热插拔电源类似时、可以看到这种快速斜坡。 使用电阻器可以降低此类事件产生的浪涌电流。 使用串联电阻和旁路电容器也会减慢器件的电源斜坡。

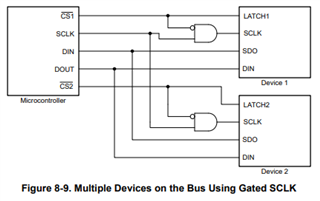

对电路的唯一其他建议更改是在 SPI 兼容总线上使用多个器件。 我们建议使用/CS 对 SCLK 进行门控。 这样、当器件未激活时、器件不会接收 SCLK。 这显示在图8-9第41页的数据表中。

吴约瑟

hide-san、

CMP 引脚连接到电压 DAC 的输出放大器中的内部节点。 这用于实现放大器稳定性的电容补偿。

如果您将 CMP 电容器从1000pF 更改为470pF、那么我认为您只应考虑几个方面。 如前所述、稳定时间将发生变化。 图7-36至7-38中显示了这种情况。 另一个变化是驱动负载电容的能力。 在 CMP 引脚上为1000pF 时、您将驱动更多的负载电容、但如果为470pF、您将获得如图7-38所示的结果。

请注意、如果您保持1000pF CMP 电容、并且添加了100pF 电容、那么无论如何、您仍可能会降低负载电容驱动能力。

吴约瑟