Other Parts Discussed in Thread: ADS54J60, TSW54J60EVM, LMH6401

主题中讨论的其他器件:ADS54J60、 LMH6401

您好!

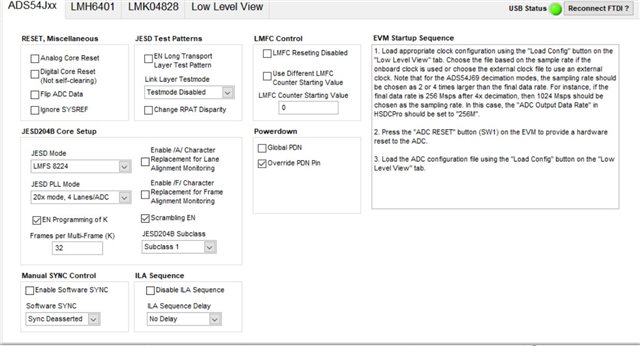

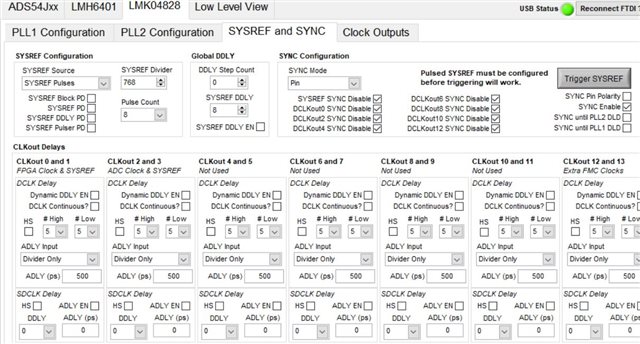

我们将 TSW54J60EVM (ADC 芯片:ADS54J60)与 Xilinx FPGA 搭配使用、以构建高速数据采集 系统。 到目前为止、我们已使 ADC 和数据通信(JESD204B)正常工作。 感谢本论坛的支持。 谢谢 Jim。

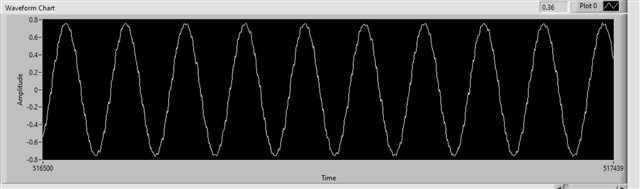

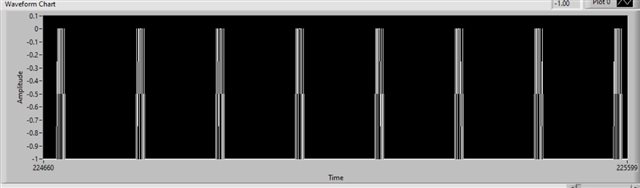

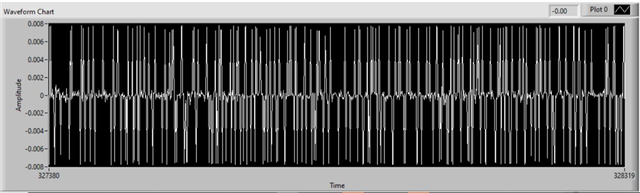

现在、我们有一个与模拟相关的问题。 在某种程度上、我们在 ADC 数据中产生了一些强尖峰噪声。 随附(图1)是噪声的屏幕截图(我们将最大读数标准化为+/- 1.0)。 噪声(+/- 0.008和+/-0.004)计数大约260次(丢失8位!)。 如果我们将输入 SMA 保持断开、或者将它们进行+/-短接、则该噪声相同(振幅和尖峰字符)。 通道 A 和通道 B 也是如此。我们花了很多时间来检查噪声源。 有人有什么建议吗? 以下是我们的谜题:

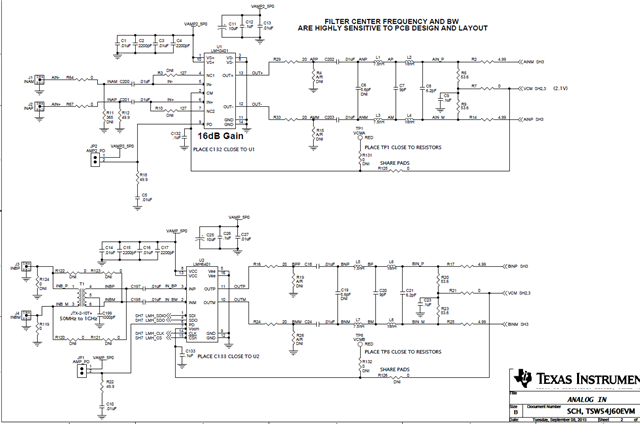

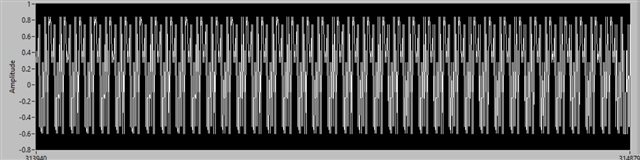

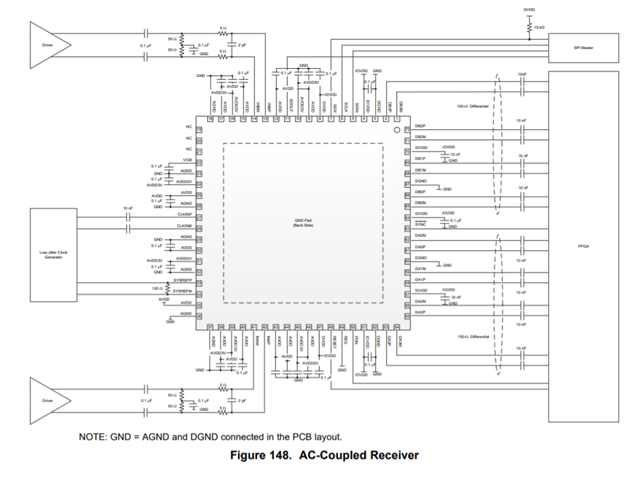

1) 1)我们认为该噪声来自数字电路。 在 TSW54J60EVM 电路板 PCB 布局上、数字接地和模拟接地似乎使用相同的 PCB 层。 在 ADC 数据表(图2)中、显示"GND=AGND 且 DGND 在 PCB 布局中已连接"。 如何避免数字接地噪声影响 ADC 数据?

2) 2)第二个数字噪声可能来自 FMC 上的 FPGA GND 信号。 这些 FPGA GND 信号位于 FMC 引脚上。 如何防止这些噪声进入 ADC 数据?

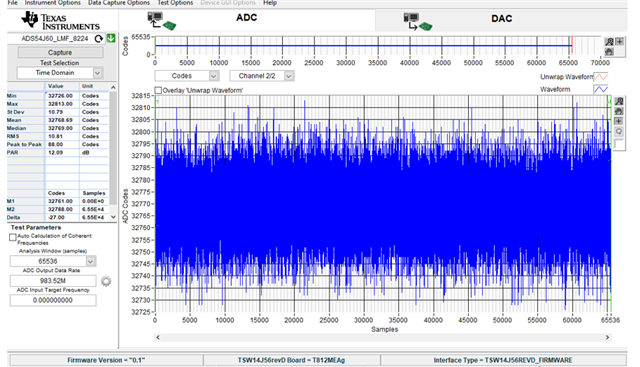

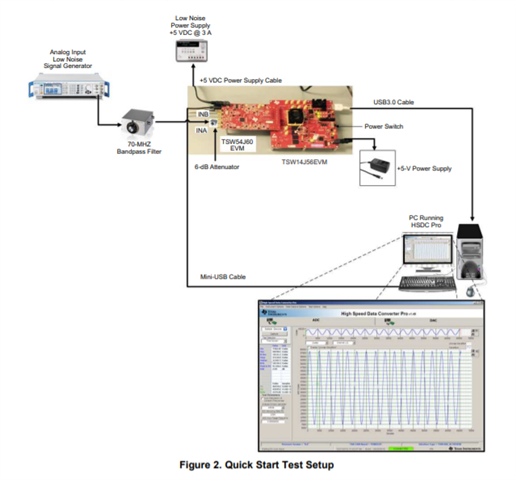

3) 3)由于我们将 TSW54J60EVM 与 Xilinx FPGA 板配合使用、因此我们没有购买 TSW54J60EVM 数据表(图3)中所示的 TSW15J56EVM。 是否有人使用 TSW54J60EVM 演示板并在 ADC 原始数据中获得真正的16位分辨率?

我们渴望解决这个噪声问题并使用具有全分辨率的芯片。 请帮帮我们。 非常感谢!

-Yuke

图1 SMA 输入开路或短接在一起时的 ADC 噪声

图2 ADC 芯片数据表显示了在 PCB 布局中连接的 AGND 和 DGND

图3 TI 建议的设置