Other Parts Discussed in Thread: ADC07D1520, DAC3151

主题中讨论的其他器件: DAC3151

尊敬的德州仪器(TI):

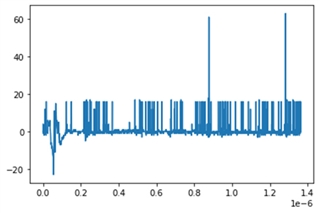

我们在由 FPGA 管理的嵌入式系统上设计了一个采用 ADC07D1520和 DAC3151的电路。 我们在处理 ADC 输出数据时遇到了一些问题。 DAC 的输出和 ADC 的输入进行级联、我们在 ADC 输入端使用示波器测量波形、正如我们编程的那样、该波形正常、但 ADC 获取的信号有点奇怪: 我们得到的信号是非正弦信号、其持续时间远小于应有的时间、例如、这应该是一个具有10个周期的20MHz 正弦波。 显然、在开始时、我们有一个信号、但它会立即消失、与20MHz 正弦波的10个周期不对应。

因此、我们将与您联系、以了解您是否可以为我们提供帮助。 在我们的项目中、ADC07D1520配置主要是:

- 双倍数据速率(DDR)支持在1.5GHz 下运行;

- 只有一个具有90º 相位的 DCLK;

- 多路解复用模式;

- 双边沿采样(DES)模式、I 通道由两个 ADC 运行。

我们将使用型号为 Z-7010的 Xilinx ZYNC-7000 FPGA 来管理 ADC 数据采样。 ADC 和 FPGA 之间的接口描述如下:

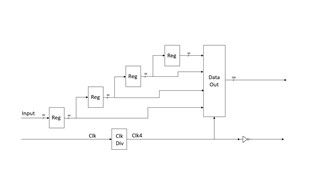

- 每个差分 ADC 输出 P 和 N 对与 Xilinx 库中的差分输入缓冲基元(IBUFDS)映射、包括应用特定时钟差分输入缓冲器(IBUFGDS)的 DCLK。 在下图中、输入缓冲器是 QD、ID、Q、I 和 Clk 模块。 Clk Up 和 Clk DN 模块是用于存储 P 和 N 级联值的锁存器、分别由 Clk 上升沿和下降沿存储。 输出数据信号是 P 和 N 采样值的串联。

后续电路是串行器模块、用于连接四个数据连续值。 它开发了一个锁存级联结构来移动连续数据值、并且数据输出信号的存储考虑到一个具有四分之一 DCLK 频率的时钟信号(Clk4)。

我们还使用 DCLK_RST 引脚将转换器与 DAC 同步、以便两个转换器都有一个公共基准帧。 在 DAC 上、硬件上存在错误、引脚连接错误、因此我们在驱动 ADC 上的 DCLK_RST 时使用 sif_sync 功能来同步转换器。 使用此功能是否会出错?

此致、Willan。