Other Parts Discussed in Thread: TSW1418EVM, TSW14DL3200EVM

主题中讨论的其他器件:TSW1418EVM、 TSW14DL3200EVM

你(们)好

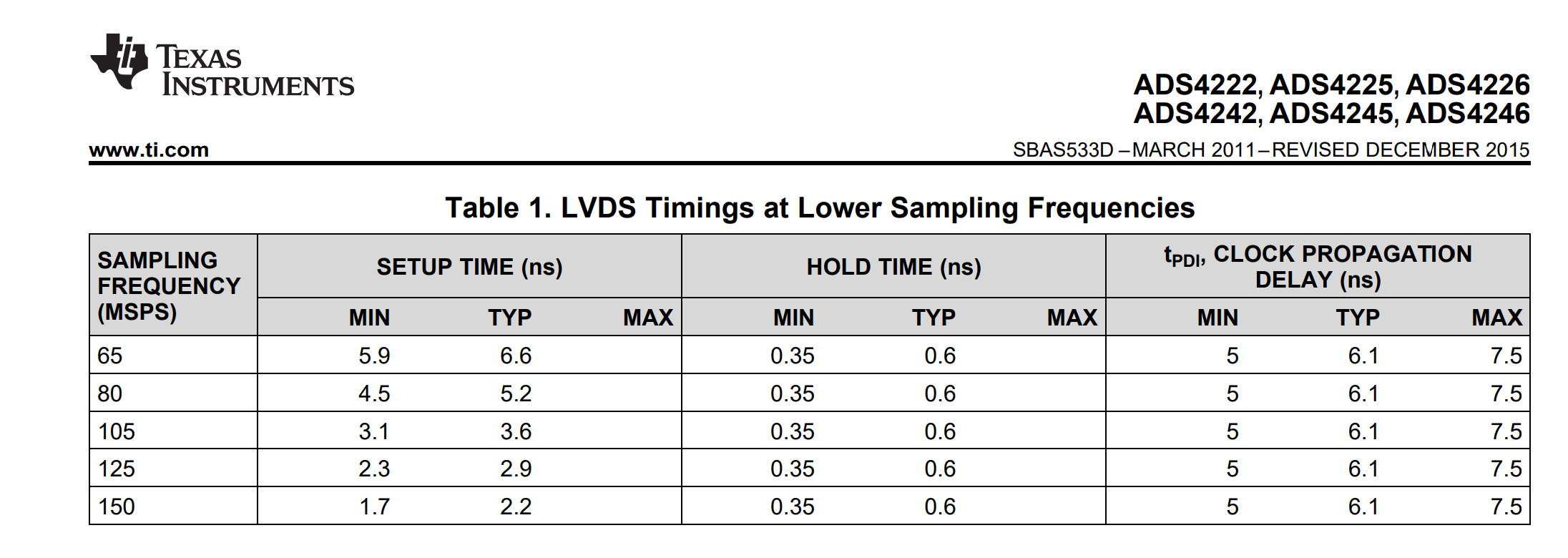

我已阅读 SLAA545 (将 Altera FPGA 连接到 ADS4249和 DAC3482 (TIDA-00069参考指南))中有关将 ADS42XX 板连接到 FPGA 开发板的说明。 我已经阅读了数据表、并放置了所需的约束条件。 但是、我的时序不好(至少可以正常工作)。 我将以大约80MSPS 的速率进行采样、因此:

create_clock -period 10.000 -name aclk -waveform {0.000 5.000} [get_ports -filter { NAME =~ "*aclk*" && DIRECTION == "IN" }]

create_clock -period 13.468 -name ADC_CLK [get_ports {FMC_LA[17]}]

create_clock -period 13.468 -name ADC_CLK_LAUNCH -waveform {3.367 16.835}

create_generated_clock -name ADC_GEN_CLOCK -source [get_pins PLLE2_BASE_inst/CLKIN1] -multiply_by 1 [get_pins PLLE2_BASE_inst/CLKOUT0]

set_input_delay -clock [get_clocks ADC_CLK_LAUNCH] -min -network_latency_included -source_latency_included -2.767 [get_ports {{FMC_LA[14]} {FMC_LA[29]} {FMC_LA[25]} {FMC_LA[24]} {FMC_LA[21]} {FMC_LA[22]}}]

set_input_delay -clock [get_clocks ADC_CLK_LAUNCH] -max -network_latency_included -source_latency_included -1.833 [get_ports {{FMC_LA[14]} {FMC_LA[29]} {FMC_LA[25]} {FMC_LA[24]} {FMC_LA[21]} {FMC_LA[22]}}]

set_input_delay -clock [get_clocks ADC_CLK_LAUNCH] -min -network_latency_included -source_latency_included -2.767 [get_ports {{FMC_LA[19]} {FMC_LA[15]} {FMC_LA[16]} {FMC_LA[11]} {FMC_LA[12]} {FMC_LA[7]}}]

set_input_delay -clock [get_clocks ADC_CLK_LAUNCH] -max -network_latency_included -source_latency_included -1.833 [get_ports {{FMC_LA[19]} {FMC_LA[15]} {FMC_LA[16]} {FMC_LA[11]} {FMC_LA[12]} {FMC_LA[7]}}]

但是、我遇到了搁置不可处理的问题。 我放置了 IODELAY 块、但保持可宽延时间是完整的。 如何正确计时 ninterface?