Other Parts Discussed in Thread: ADS4225EVM, ADS4225

主题中讨论的其他器件: SD1983EVK、 ADS4225

你(们)好

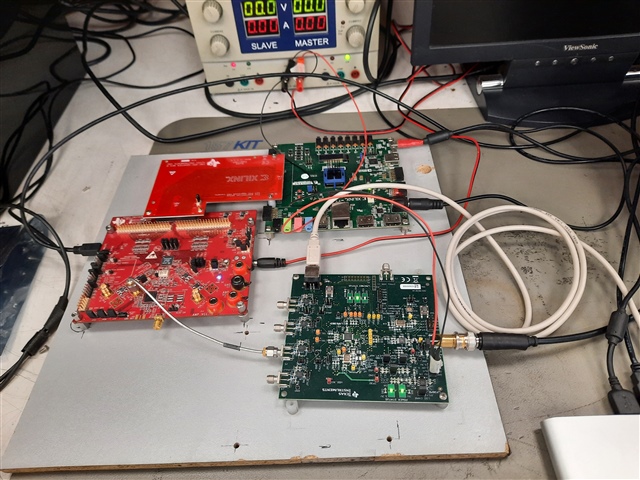

从 ADS4225EVM 获取信号时遇到一些问题。 这是设置:

该 STUP 由以下部分组成:

- SD1983EVK

- ADC-FMC 适配器

- ADS4225EVM

- Nexys 视频(基于 Xc7-a200t)

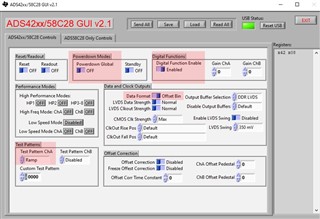

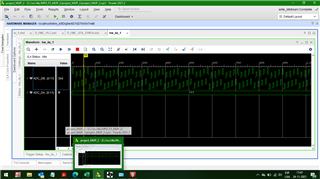

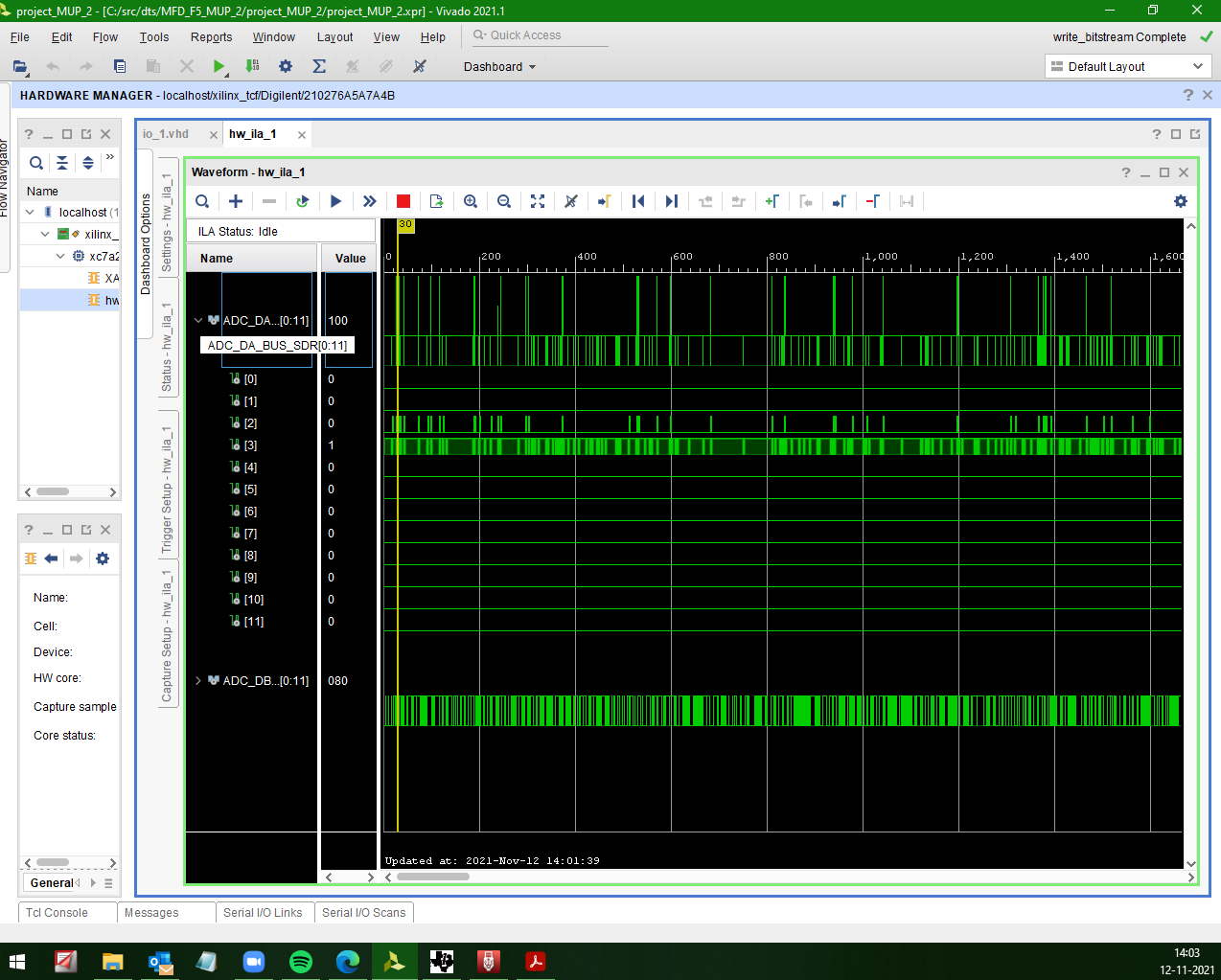

我只得到第三位和第四位、但没有其他位。 我不知道为什么会发生这种情况。 电路板具有默认设置、并使用我放置在斜坡波形发生器上的软件。 我将获得以下结果、而不是斜坡:

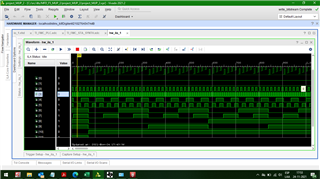

我做了一个仿真、我希望看到如下所示的内容:

我还确保 FPGA 侧的 FMC 电压选择器设置正确(1.8V)、并且映射显然正常。 下表:

| ADC-FMC | Nexys 视频 | ||||

| ADC ADS42XX | J2 | J1 | FPGA | ||

| IO_0P | 不适用 | G9. | FMC_LA_03_P | ||

| IO_0N | 不适用 | G10. | FMC_LA_03_N | ||

| IO_1P | DB12. | G12. | FMC_LA_08_P | ||

| IO_1N | DB12. | G13. | FMC_LA_08_N | ||

| IO_2P | DB10 | 问题13. | FMC_LA_07_P | ||

| IO_2N | DB10 | H14. | FMC_LA_07_N | ||

| IO_3P | DB8. | G15. | FMC_LA_12_P | ||

| IO_3N | DB8. | G16. | FMC_LA_12_N | ||

| IO_4P | DB6 | H16. | FMC_LA_11_P | ||

| IO_4N | DB6 | H17. | FMC_LA_11_N | ||

| IO_5P | DB4. | G18. | FMC_LA_16_P | ||

| IO_5N | DB4. | G19. | FMC_LA_16_N | ||

| IO_6P | DB2 | H19. | FMC_LA_15_P | ||

| IO_6N | DB1 | H20. | FMC_LA_15_N | ||

| IO_7P | DB0 | H22. | FMC_LA_19_P | ||

| IO_7N | DB0 | H23. | FMC_LA_19_N | ||

| IO_8P | DA12. | G21. | FMC_LA_20_P | ||

| IO_8N | DA12. | G22. | FMC_LA_20_N | ||

| IO_9P | DA10 | G24. | FMC_LA_22_P | ||

| IO_9N | DA10 | G25. | FMC_LA_22_N | ||

| IO_10P | DA8. | H25 | FMC_LA_21_P | ||

| IO_10N | DA8. | H26. | FMC_LA_21_N | ||

| IO_11P | DA6. | H28 | FMC_LA_24_P | ||

| IO_11n | DA6. | H29 | FMC_LA_24_N | ||

| IO_12P | DA4. | G27. | FMC_LA_25_P | ||

| IO_12N | DA4. | G28 | FMC_LA_25_N | ||

| IO_13P | DA2 | C18. | FMC_LA_14_P | ||

| IO_13N | DA2 | C19. | FMC_LA_14_N | ||

| IO_14P | DA0 | H31. | FMC_LA_27_P | ||

| IO_14N | DA0 | H32. | FMC_LA_27_N | ||

| IO_15P | D26. | FMC_LA_28_P | |||

| IO_15N | D27. | FMC_LA_28_N | |||

| IO_16P | G33. | FMC_LA_31_P | |||

| IO_16N | G34. | FMC_LA_31_N | |||

| IO_17P | G36. | FMC_LA_33_P | |||

| IO_17N | G37 | FMC_LA_33_N | |||

| IO_18P | H7 | FMC_LA_02_P | |||

| IO_18N | H8. | FMC_LA_02_P | |||

| IO_19P | H10. | FMC_LA_04_P | |||

| IO_19N | H11. | FMC_LA_04_N | |||

| IO_20P | C10. | FMC_LA_06_P | |||

| IO_20N | 问题11. | FMC_LA_06_N | |||

| IO_21P | D11. | FMC_LA_05_P | |||

| IO_21N | D12. | FMC_LA_05_N | |||

| IO_22P | C14. | FMC_LA_10_P | |||

| IO_22N | C15 | FMC_LA_10_N | |||

| IO_23P | D23. | FMC_LA_23_P | |||

| IO_23N | D24 | FMC_LA_23_N | |||

| IO_24P | C26. | FMC_LA_27_P | |||

| IO_24N | C27. | FMC_LA_27_N | |||

| IO_25P | G30 | FMC_LA_29_P | |||

| IO_25N | G31. | FMC_LA_29_N | |||

| IO_26P | H34 | FMC_LA_30_P | |||

| IO_26N | H35. | FMC_LA_30_N | |||

| IO_27P | H37 | FMC_LA_32_P | |||

| IO_27N | H38. | FMC_LA_32_N | |||

| FCLKP | G6 | FMC_LA_00_P | K18. | ||

| FCLKN | G7 | FMC_LA_00_N | K19. | ||

| DCLKP | D20. | FMC_LA_17_P | |||

| DCLKN | D21. | FMC_LA_17_N | |||

| SDATA | D17. | FMC_LA_13_P | |||

| SCLK | D18. | FMC_LA_13_N | |||

| SPI_1 | D14. | FMC_LA_09_P | |||

| 传感器 | D15. | FMC_LA_09_N |

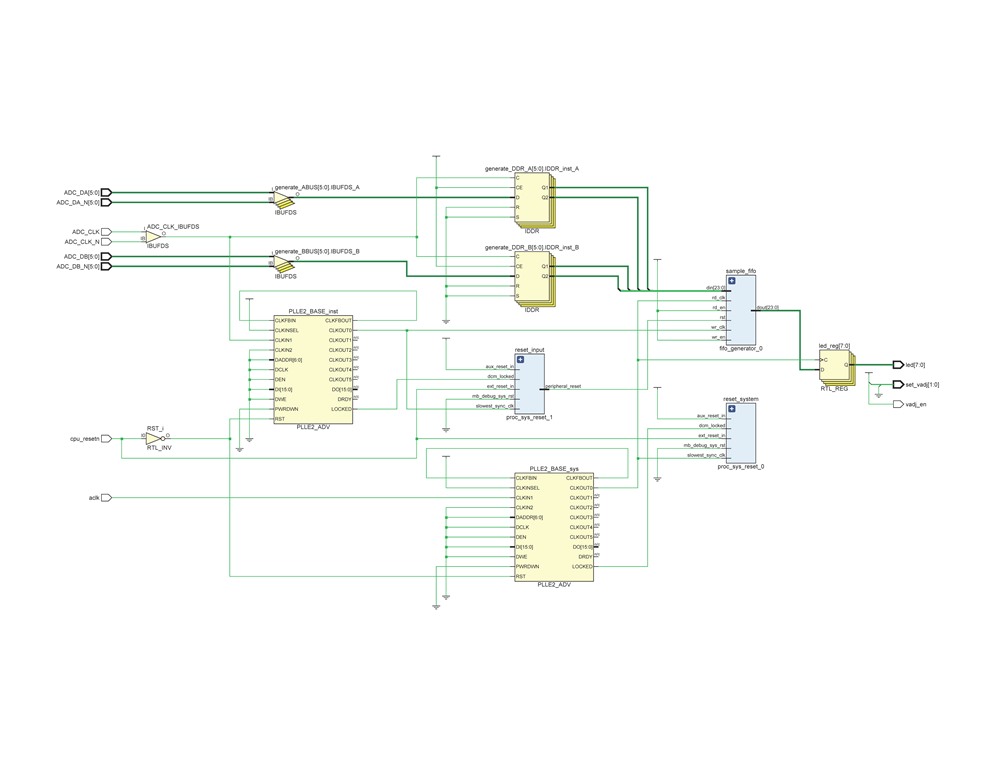

这里是我用于将其数字化的 RTL 图:

我们欢迎您提出任何有关获得正确信号的建议

谢谢