Other Parts Discussed in Thread: ADC12DJ3200, LMK04828, ADC12DJ3200EVM

主题中讨论的其他器件: LMK04828、

您好!

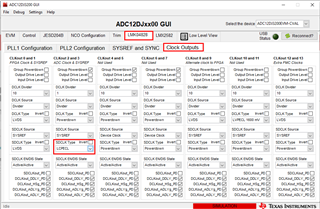

我按如下方式配置了 ADC12DJ3200:

0x0000 0xB0 //进行软复位

延迟100ms

0x0200 0x00 //清除 JESD_EN (始终在 CAL_EN 之前)

0x0061 0x00 //清除 CAL_EN (始终位于 JESD_EN 之后)

0x0201 0x00 //设置 JMODE0

0x0202 0x03 //设置 KM1=3、因此 K=4

0x0204 0x05 //使用 TMSTP+/-输入、偏移二进制数据、启用扰频器

0x0205 0x04 //斜坡测试模式

0x003B 0x03 //启用 TSTP 接收器和 TSTP LVPECL

0x0213 0x07 //启用超范围,将超范围保持设置为最大周期8*2^7=1024个样本

0x0048 0x03 //将串行器预加重设置为3

0x029 0x30 //启用 SYSREF 接收器电路并设置缩放位

读取0x02C-0x2E

0x029 0x74 //设置 SYSREF_PROC_EN 和 SYSREF_SEL

0x0061 0x01 //设置 CAL_EN (始终在 JESD_EN 之前)

0x0200 0x01 //设置 JESD_EN (始终在 CAL_EN 之后)

0x006C 0x00 //将 CAL_SOFT_TRIG 设置为低电平以复位校准状态机

0x006C 0x01 //将 CAL_SOFT_TRIG 设置为高电平以启用校准

在参考设计中将 MASTER_RESET_n 信号设置为‘1’并将 Rx_SYNC_RESET_VIO 信号设置为‘0’后,寄存器0x0208和0x02C1中的值如下:

0x0208 = 0x0C

0x02C1 = 0x08

因此、似乎没有建立 JESD204链路

你对我有什么建议吗?

BR

Chris