您好!

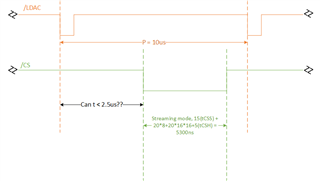

关于 DAC81416、/LDAC 和下一个数据更新周期/CS 之间是否有任何时序要求? ASK 之所以是因为当我们缩短/LDAC 和/CS 之间的时间时、DAC81416的某些通道无法按预期输出波形。

在我们的设计中、我们使用不同 DAC 的 LDAC 信号来同步不同通道、不同 DAC 上的输出电压。 我们满足了数据表中描述的 tLOGDLY (cs 上升沿到 LDAC 下降沿)要求、实验的详细信息如下:

首先、LDAC 上升沿到 CS 下降沿(新一轮数据传输)为:DAC0 150ns、DAC1 790ns、DAC2 1430ns。 那么 DAC0的大多数通道将不工作、只有一个或两个通道能够输出正确的波形。 DAC1通道2~15可以输出正确的波形,通道0和1将不起作用(只能输出固定电压,猜猜是波形的第一个点)。 DAC 2都正常。

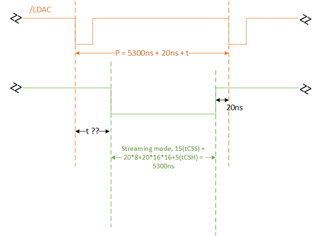

然后、我们将 DAC0和1的传输延迟到1430ns (LDAC 上升沿到其自己的 CS 下降沿)。 所有 DAC 的所有通道都很好。

然后、我们尝试更早地放置 DAC 0和1、但仍然满足数据表9.3.1.2.1章中所述的1us 等待时间。

3.1 DAC0 1030ns (LDAC 上升沿至其自己的 CS 下降沿)、DAC1 1190ns。 那么、只有 DAC0的 CH1 (第二通道)不起作用(猜只输出波形的第一个点)、DAC0的其他15个通道都很好。 DAC 1和2均正常。

3.2 DAC0之后为1140ns、DAC 1 1270。 与3.1相同、只有 DAC0的 CH1无法正常工作、其余都很好。

3.3 DAC0之后为1190ns (与 DAC1在3.1中的时间相同)、DAC 1 1300ns。 同样、只有 DAC0的 CH1无法正常工作、其他都很好。

BR/Wang Peng