主题中讨论的其他器件: TMS320F28335、 ADS8568

我对 ADS8528上的 SPI 时钟极性和相位感到困惑。

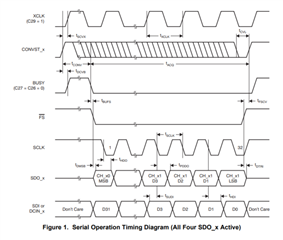

在数据表(SBAS543C、第33页)中、它说:

从最高有效位(MSB)开始、输出数据随着 SCLK 下降沿而改变。

串行数据输入 SDI 在 SCLK 下降沿锁存。

从 MCU 的角度来看:

- MCU 在上升沿输出数据,因为 ADS8528在下降沿锁存数据

-由于 ADS8528在下降沿输出数据,因此 MCU 在上升沿锁存数据

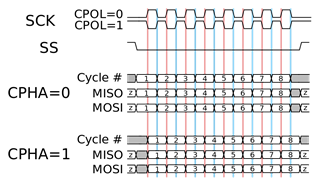

下面是 TMS320F28335支持的时钟方案(SPRUI07、第558页):

下降沿。 SPI 在下降沿发送数据、在 SPICLK 的上升沿接收数据。

具有延迟的下降沿。 SPI 在下降沿前半个周期发送数据、在 SPICLK 的下降沿接收数据。

无延迟的上升沿。 SPI 在上升沿发送数据、在 SPICLK 的下降沿接收数据。

具有延迟的上升沿。 SPI 在上升沿前半个周期发送数据、在 SPICLK 的上升沿接收数据。

这是否意味着我必须在写入配置后更改主器件(MCU)的时钟方案? 更具体地说:

-要将配置写入 ADS8528、我将使用下降沿和延迟

-要从 ADS8528读取配置和数据,我将立即使用下降沿

数据表中没有提到这一点、但从图中我假设串行时钟应该在高电平空闲。 这就是为什么我只提到"下降沿"时钟方案的原因。 如果我错了、请纠正我的问题。

这是我第一次需要更改读取和写入操作的时钟方案。 请确认此结论吗?

如果我对此回答正确、那么在 ADS8528上实施此计时方案的原因是什么? 为什么不对读取和写入操作使用单个时钟方案?

让我先从某种角度了解一下我是如何实现这一点的。

我首先将时钟方案配置为适用于"写入配置"。 我使用相同的时钟方案读回配置、直到我在代码中进行了一些与 SPI 无关的微小更改。

我说它不起作用的意思是、我读回的配置不符合预期。 整个配置似乎被位移向左边2。 再说一次、只有当我在代码中进行了一些与 SPI 无关的微小更改时、这个问题才会出现。

然后、我再次阅读 ADS8528的数据表、并认为读取和写入操作的时钟方案是不同的。 我 实施了这种新逻辑 、似乎可行、但我仍想得到确认。