您好!

我们在设计中使用 DAC81416、DAC 配置为单端模式、输出范围为0~20V。

我们计划使用清晰的 DAC 功能来强制 DAC 输出0V。

在数据表中、当/CLR 引脚处于活动状态时、输出应强制为零代码(在我们的配置中为0V)、但在我们的设计中、当/CLR 引脚 acitve (低电压)时、输出保持为20V、而不是预期的零代码(0V)。

是否有其它配置需要使 CLEAR 功能正常工作?

BR/Wang Peng

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们在设计中使用 DAC81416、DAC 配置为单端模式、输出范围为0~20V。

我们计划使用清晰的 DAC 功能来强制 DAC 输出0V。

在数据表中、当/CLR 引脚处于活动状态时、输出应强制为零代码(在我们的配置中为0V)、但在我们的设计中、当/CLR 引脚 acitve (低电压)时、输出保持为20V、而不是预期的零代码(0V)。

是否有其它配置需要使 CLEAR 功能正常工作?

BR/Wang Peng

您好!

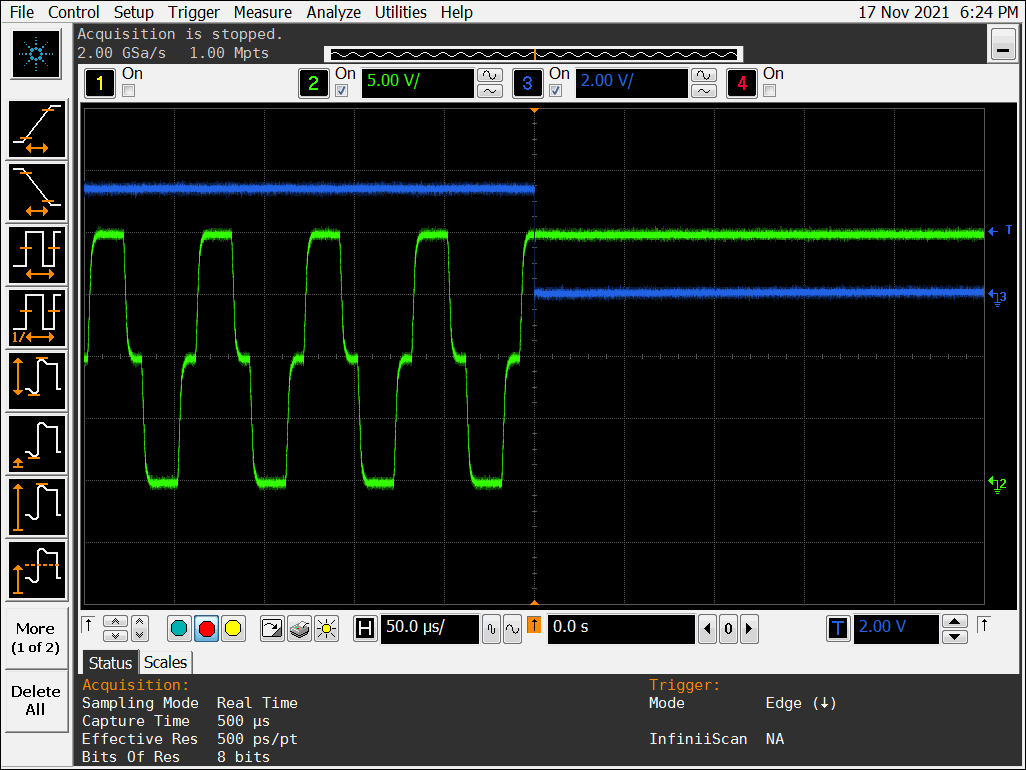

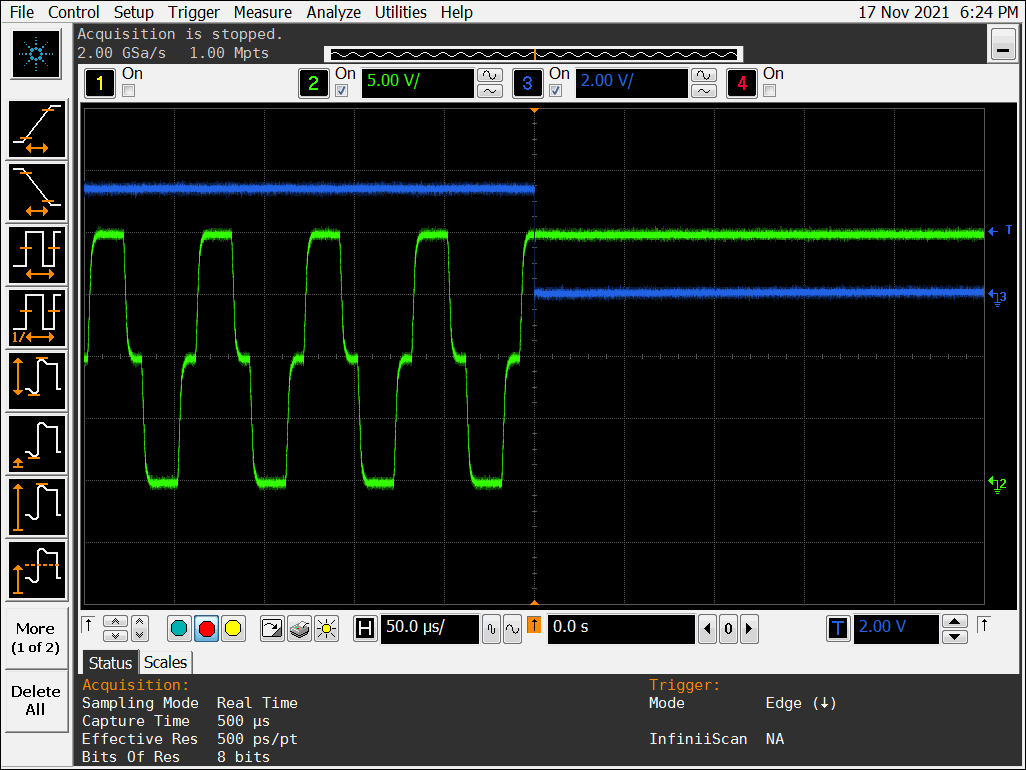

Bule 为/CLR。

DAC 配置有7个基本步骤:

1.配置 SPIC委 会为 DAC 器件上电并启用流模式。 将 x"0A8C"写入地址03。

2.配置 SYNCCONFIG 以启用同步输出模式。 将 x"FFF"写入地址06。

3-6. 配置 DACRANGEn 将输出范围设置为0~20V。 将 x"22222"分别写入地址0A、0B、0C、0D

7. 将 DACPWDWN 配置为相应的单通道上电。 将数据从 CPU (通道启用)写入地址09。

配置后、每个基本周期向 DAC 地址10发送数据、并在传输后将 LDAC 引脚置为有效。 数据更新周期为10us。

在 LDAC 引脚置位约60ns 后、清零信号可能会在基本周期结束时生效。

BR/Wang Peng