主题中讨论的其他器件:ADC12DJ3200、 LMK04828

你(们)好

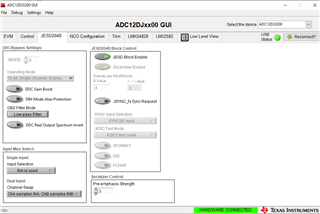

我使用的 ADC12DJ3200在 JMODE 0下工作、Fs=1250 MSPS。 串行器/解串器的运行速率为5Gbps。 从 LMK04828生成的 FPGA 时钟为125MHz (DCLK=10)。 我正在使用 ADC 内部测试模式模式图形进行测试。 下面是 ADC GUI 中 JESD204B 设置的屏幕截图:

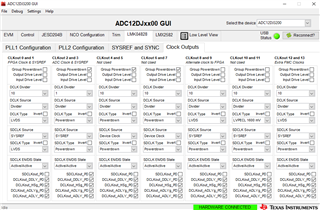

LMK04828时钟输出设置为:

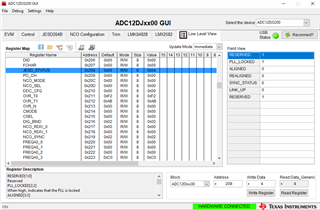

但是、当我使用这些设置对 ADC 器件进行编程时、我的 JESD 链路状态不会上升。 同步信号也始终为低电平、如下所示

我在这里丢失了什么吗? 期待您的回复。

此致

Rohit