您好、先生、

我现在有一个 PIN 数组。 我想选择一个 ADC 来收集 PIN 信号。

我想将该阵列放入摄像头接口中。

4个通道、12位或更高。

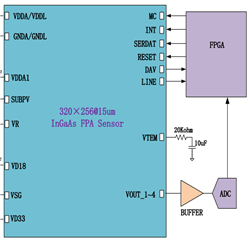

这是供应商提供的参考。

它是单端输入。

我读取了您的 ADC3422、想知道它是否可以应用于我的应用。

如果 ADC3422 可用于我的应用、

我的问题是:

如何在单端信号和 CLK 单端信号中进行连接? CLK 由 FPGA 输出?

2. CLK 是否只需要单端输出? 是否需要隔离耦合电容器?

如果不是、您会推荐什么?

感谢您的澄清。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、先生、

我现在有一个 PIN 数组。 我想选择一个 ADC 来收集 PIN 信号。

我想将该阵列放入摄像头接口中。

4个通道、12位或更高。

这是供应商提供的参考。

它是单端输入。

我读取了您的 ADC3422、想知道它是否可以应用于我的应用。

如果 ADC3422 可用于我的应用、

我的问题是:

如何在单端信号和 CLK 单端信号中进行连接? CLK 由 FPGA 输出?

2. CLK 是否只需要单端输出? 是否需要隔离耦合电容器?

如果不是、您会推荐什么?

感谢您的澄清。

您好!

是的、您可以使用单端输入。

1.对于单端时钟、与差分输入时钟相比、不应对性能产生明显影响。 但是、来自 FPGA 的时钟很可能具有高 rms 抖动(可能在毫微秒内)。 最佳值以 femto 秒为单位、以匹配 ADC 的孔径抖动。) 由于您正在捕获摄像头输出(改变直流电平)、我认为这不会对性能产生太大的影响。

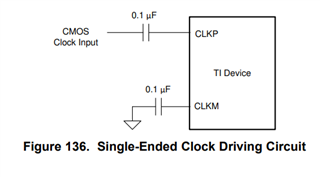

采样时钟在内部偏置。 CLKP 的输入端需要一个交流耦合电容器、CLKM 上也需要一个连接到 GND 的交流电容器。

2.对于单端模拟输入、由于仅使用一半的 ADC 输入、信号功率/动态范围将会有3dB 的损耗。 单端信号将进入 AINP (在 VCM 处偏置)、而 AIN 将被偏置至 VCM (+0.95V)。 VCM 是 ADC 的输出、是模拟输入范围的中标度值。

我有兴趣了解客户应用要求、因此如果您想进一步讨论、请随时向我发送电子邮件。

此致、

Dan