您好!

我在电路板上使用4个 ADS1256 IC。 第1 个 IC 配置为读取 一个差分通道、第4个 IC 配置为4个单端通道。

所有差分通道都经过编程、可实现连续循环。 编程的其余单端通道使用多路复用器循环。

CLKIN 为7.68MHz、SCLK 为1.92MHz、对于连续循环和多路复用循环、DRATE 均设置为3750。

连续循环的程序序列为:

1) 1)在 DRDY 的下降沿发出 SDATAC 命令。

2)在 DRDY 的下一个下降沿更新状态寄存器(hx00) 、然后延迟5微秒

3) 3)更新 ADCON 寄存器 (hx00) 、然后延迟5微秒

4)更新 DRATE 寄存器 (hxC0)、然后延迟5微秒

5) 5)在 DRDY 的下一个下降沿发出 SELFCAL 命令、然后延迟5微秒

6) 6)在 DRDY 的下一个下降沿更新多路复用器寄存器(hx01)

7) 7)在 DRDY 的下一个下降沿发出 RDATAC 命令 、然后延迟8 微秒

8) 8)读取 DOUT (24位)

9) 继续在 每个 DRDY 的下降沿读取 DOUT (24位)

所有3个差分通道上的观察和问题

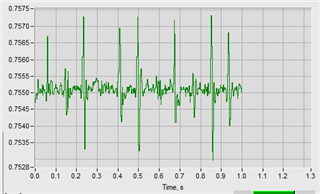

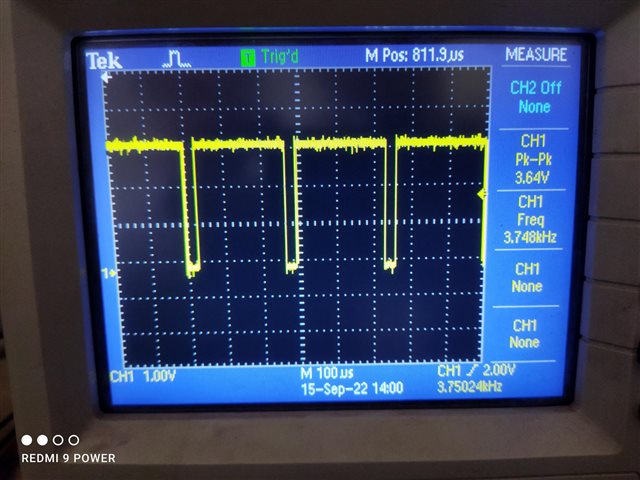

1) 1)确认所需的 DRATE 在示波器上设置、高电平时间为2.5微秒、并在 DRDY 周期的剩余时间内保持低电平。

2) 2) SCLK 根据 程序序列生成24个脉冲、周期为0.52微秒

3) 3) DOUT 始终保持高电平、因为我们无法正确读取该值。 请帮助我们 解决此问题

具有4个单端通道的第4个 IC 的多路复用循环的程序序列为:

1) 1)在 DRDY 的下降沿发出 SDATAC 命令。

2)在 DRDY 的下一个下降沿更新状态寄存器(hx00) 、然后延迟5微秒

3) 3)更新 ADCON 寄存器 (hx00) 、然后延迟5微秒

4)更新 DRATE 寄存器 (hxC0)、然后延迟5微秒

5) 5)在 DRDY 的下一个下降沿发出 SELFCAL 命令、然后延迟5微秒

6)在 DRDY 的下一个下降沿更新多路复用器寄存器(对于第二个 SE-Ch 为 hx81) 、然后延迟5微秒

7) 7)依次发出 SYNC、WAKEUP、RDATA 命令、然后延迟8 微秒

8) 读取 hx80第一个 SE-Ch 的 DOUT (24位)

9) 9)在 DRDY 的下一个下降沿更新多路复用器寄存器(第三个 SE-Ch 为 hx82) 、然后延迟5微秒

10) 10)依次发出 SYNC、WAKEUP、RDATA 命令 、然后延迟8 微秒

11) 11)读取 hx81 第二个 SE-Ch 的 DOUT (24位)

12)在 DRDY 的下一个下降沿更新多路复用器寄存器(第三个 SE-Ch 为 hx83) 、然后延迟5微秒

13) 13) 依次发出 SYNC、WAKEUP、RDATA 命令 、然后延迟8 微秒

14) 读取 hx82第三 个 SE-Ch 的 DOUT (24位)

15)在 DRDY 的下一个下降沿更新多路复用器寄存器(第一个 SE-Ch 为 hx80) 、然后延迟5微秒

16) 16) 依次发出 SYNC、WAKEUP、RDATA 命令 、然后延迟8 微秒

17) 读取 hx83 第三 个 SE-Ch 的 DOUT (24位)

所有3个差分通道上的观察和问题

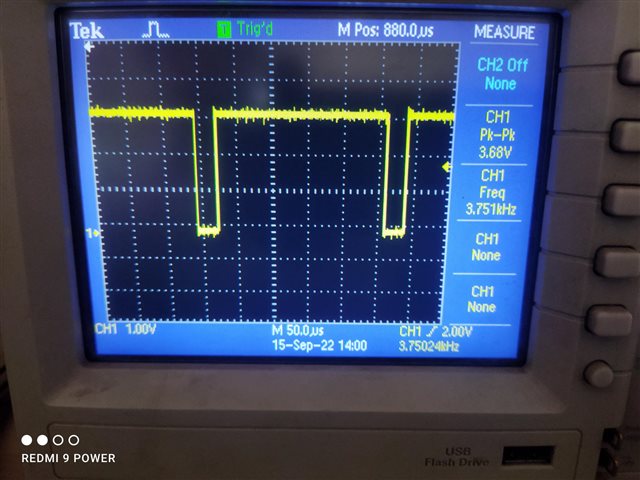

1) 1)确认所需的 DRATE 在示波器上设置、高电平时间为2.5微秒、并在 DRDY 周期的剩余时间内保持低电平。

2) 2)正确生成 SCLK (根据读取和写入操作期间的程序序列) 24个 脉冲、周期 为0.52微秒

3) 3)发现 DIN 为编程序列。

4)但是、DOUT 信号在 T6延迟后不会立即出现、而是仅在 DRDY 处于低电平时(即 DIN 处于活动状态)才会出现 RDATA 命令。 尽管第一个命令问题是 SDATAC、但看起来连续模式仍然处于活动状态。 请帮助我们解决该问题。

我们从很长时间以来一直在努力解决这些问题。 我们将感谢您立即提供帮助。

此致、

Somayya