我想通过硬件电路复位 DAC、将 nRST 拉至低电平、RSTSEL 连接至5V、

但 DAC 输出保持不变、而不是复位到中标度,这意味着 DAC 未复位、原因?以及如何解决该?

信号从 CPLD 中发出、然后通过光耦合器隔离器件发送到 DAC。

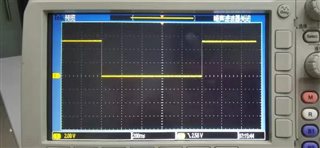

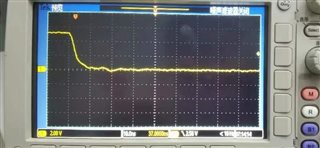

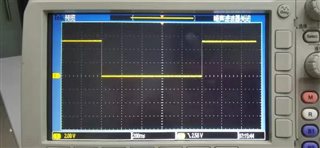

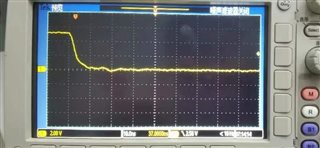

下图是复位信号

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我想通过硬件电路复位 DAC、将 nRST 拉至低电平、RSTSEL 连接至5V、

但 DAC 输出保持不变、而不是复位到中标度,这意味着 DAC 未复位、原因?以及如何解决该?

信号从 CPLD 中发出、然后通过光耦合器隔离器件发送到 DAC。

下图是复位信号

谢谢!

您好、Yang、

让我再问几个后续问题、这些问题可能会帮助我进行调试:

示波器上显示的测量是在哪里进行的、是直接在引脚上还是在其他地方进行的? 如果在其他位置进行了测量、您可以重新进行测量、但直接在引脚上检查输出。

当您提到用接地线触摸复位信号时、此接地线来自何处?

您的器件和控制器之间是否有统一的接地? 如果没有、请尝试将两个器件连接到同一接地端、然后重试。

为了回答您的问题、复位信号是电平触发的。

谢谢、

Illia Volkov

您好、Yang、

复位信号没有下降沿要求、因为它是电平触发的。 此外、我认为 SPI 通信不应干扰复位、通过查看原理图、所有连接和信号看起来都是正确的。 关键点是、如果引脚对地短路、器件会正常复位。 这让我相信问题来自其他地方提供的复位信号。 除此之外,我看不到其他任何明显的问题会导致这种行为。 让我与我的设计团队跟进、看看他们是否可以帮助解决这个问题。

谢谢、

Illia Volkov

您好、Yang、

其他一些可能有用的东西:

只需确保、当您测量复位信号时、 您将示波器的接地探针连接到 DAC 的接地端子、对吧? 如果没有、请尝试将上述探针连接到 DAC 的接地端、并通过这种方法测量复位信号、以确认 DAC 确实将其视为"低电平"。

另一个建议是确保所有数字线路都由数字信号供电。 我看到上拉至复位控制线由模拟信号供电、请尝试将其连接到数字电源。 这也可能会影响这样的行为。

我认为可能导致此类行为的因素之一是、光耦合器可能会在处于关断状态时灌入电流。 您能否 在线路断开时测量 nRST 引脚上的电流、以查看电流是否已断开。 如果该值较高、则可能会导致问题。 甚至可以尝试更换光耦合器、看看这是否可以解决问题。

此外、为了澄清这一点、您的 nRST 线路上拉电阻器的值是多少? 如果不是、您能否尝试将该电阻器替换为3.3k 欧姆至10k 欧姆的电阻器、看看这是否有用?

请告诉我这些操作是否有帮助。

谢谢、

Illia Volkov