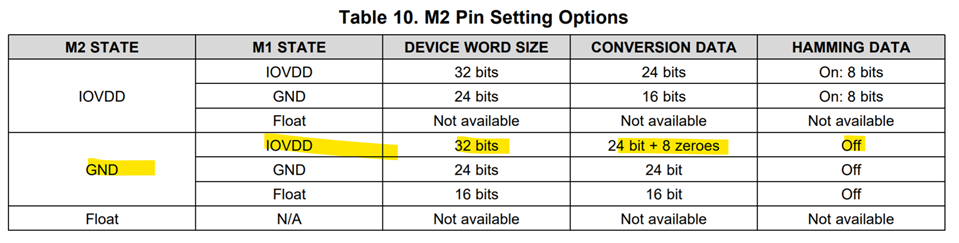

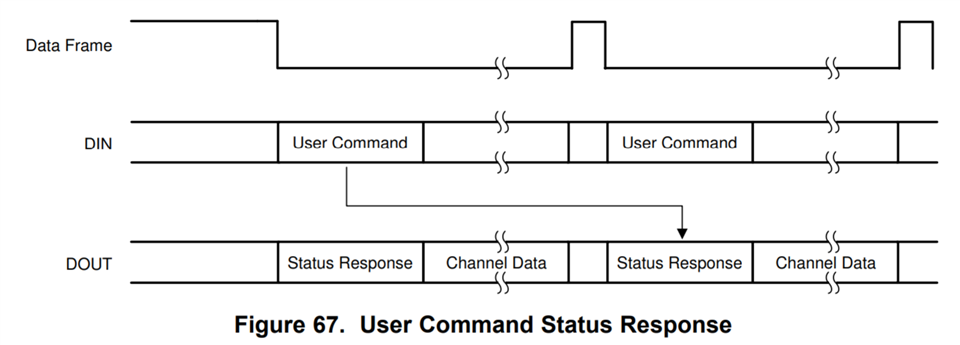

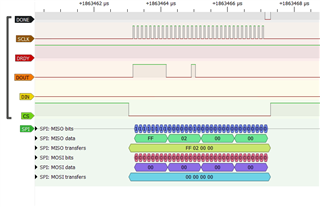

我在异步从模式下使用 ADS131a02、32位器件字、汉明码字验证关闭。 初始化正确进行。 我获取的状态为0x2220至 NULL 命令、当我读取 STAT_S 寄存器时、它提供的状态为0x2501。 我正在传递 SCLK 的96位(状态+ 32位、通道1 + 32位、通道2)。 我还通过传递80位(通道状态为16位+通道为32位+通道为1位+ 32位)进行了检查、但仍然面临相同的问题。 SPI 主器件的 SCLK 设置为26MHz 频率。 如果我将 SCLK 频率增加到高于26MHz、ADS131a02将不会响应。 有关如何解决问题的任何输入。