主题中讨论的其他器件: TLV9064、 REF5025

您好!

我们使用 ADS8528进行开发。 同样、我们对接口和功能有一些疑问。

我们将在开发板中使用 ADS8528、其配置如下:

- 硬件模式

- 所有 CONVST_x 连接在一起

- 外部 Vref

- 内部时钟

- 在串行模式(SPI)下通过 SDO_A 和 SDI 线路进行数据收集。

- 不处于菊花链模式。 为每个 ADC 选择单独的芯片

- 使用的全部3个 ADC

对于上述配置、以下是有关 ADS8528功能的查询、

在硬件模式下使用时、所有 CONVST_x 都连接在一起、BUSY/INT (位27)在 INT 模式下运行。 为了进行配置 、我们是否需要在 SW 模式下使用 SPI 线路配置配置配置寄存器? 还可以更改 INT (位 C26)的极性

2、 现在根据第1点、我们需要将硬件/软件引脚更改为软件模式。 现在、由于 ADC 处于 SW 模式、ADC 上其他引脚的状态是什么、例如 RANGE / XCLK? 由于在 HW 模式下、范围配置为2xVREF = 5V 双极输入、但在 SW 模式下、该引脚充当外部 XCLK 信号。 在这种情况下、如何在 ADC 保持 SW 模式期间定义范围? 配置寄存器更新完成后、当器件恢复到硬件模式时、它是否会根据配置寄存器进行更改并重新初始化?

在 数据表的第16页中、tXCLK 被称为66.67ns、每次转换的时钟周期为19-20个周期。 因此、转换时间 tCONV=1.33us。 但在硬件模式下、默认情况下、器件使用内部时钟 CCLK 进行转换、数据表中未提及 tCCLK。 它是否与 tXCLK 相同?

ADS8528上的绝对最大模拟输入范围为 HVSS-0.3V 至 HVDD+0.3V。 在第9页中、HVDD 建议的最小电压被指定为5V、但是电气特性被定义为 HVDD=15V 和 HVSS=-15V。 由于在我们的设计中、我们使用的是 HVDD=5V、HVSS=0V、因此当 HVDD 处于建议的最小电压时、性能会下降什么? 尽管 TLV9064电源轨已更改为5V、但 ADC 输入将限制为低于上电源轨至少100个 ADC 计数。 在这种情况下是否会对性能产生影响?

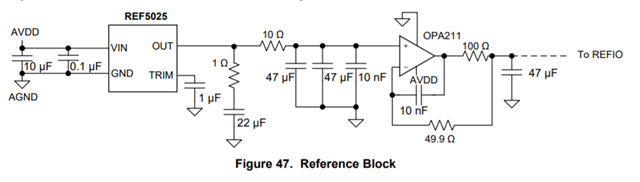

另请参阅随附的所有 ADC 和基准(Vref)电路(w.r.t)的更新原理图、然后查看相同的配置并尽快恢复。

e2e.ti.com/.../Schematic-for-TI-review.pdf

此致、

Manish Sharma