主题中讨论的其他器件:DAC38J84

您好!

我将 DAC38J84与 Arria10开发板搭配使用、目前 JESD 部件工作正常。 但是、在该 DAC 上使用 NCO 时遇到问题。 对于我的项目、我计划使用 NCO 将输入频率更改为更高的频率、我需要真正控制 NCO 输出的相位、 也就是说、在使用器件时钟和插值的情况下、我需要在 NCO 复位生效和 NCO 输出相位复位之间保持恒定的时间。

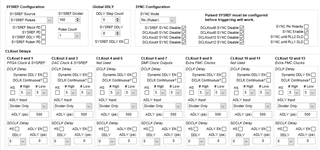

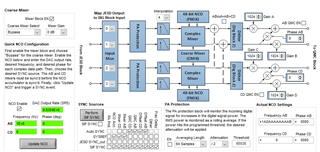

为此、我使用混音器 AB、混音器 CD 和 NCO Acc 上的 SYSREF 同步源。 以下是我正在执行的测试的步骤:

- 使用包含 JESD204b TX 的图像对 FPGA 进行编程。

- 在 EVM 和 FPGA 之间建立 JESD 链路。

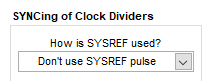

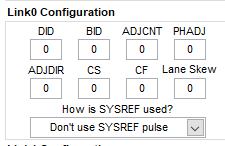

- 建立链路后、禁用与时钟分频器和与 JESD 链路0同步的 SYSREF

- 将脉冲发生器更改为仅1个脉冲

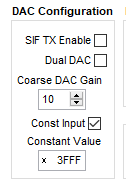

- 使用 DAC 选项的恒定输入

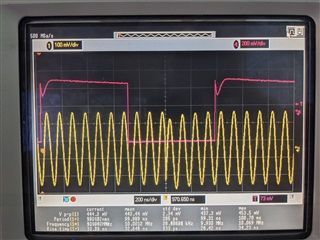

- 配置 NCO

- 使用 EVM 上的 Sysref 触发按钮创建 SYSREF 脉冲。

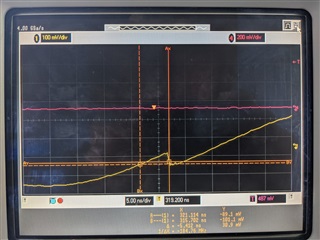

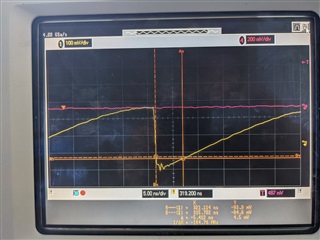

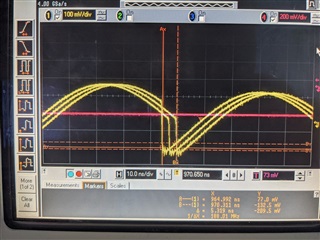

- 使用 SYSREF 脉冲的下降沿作为触发器并捕获 DAC A 输出。

- 监控下降沿触发点与 输出正弦相位中断点之间的时间。

这样、时间似乎有很大的变化(高达10ns)。 这是否符合 EVM 的预期? 这是由于评估板上 SYSREF 的交流耦合造成的吗? 是否有办法在 sysref 和 NCO 相位输出复位之间保持恒定时间?

谢谢!