主题中讨论的其他器件: REF5025、 OPA2350、 OPA350

尊敬的团队

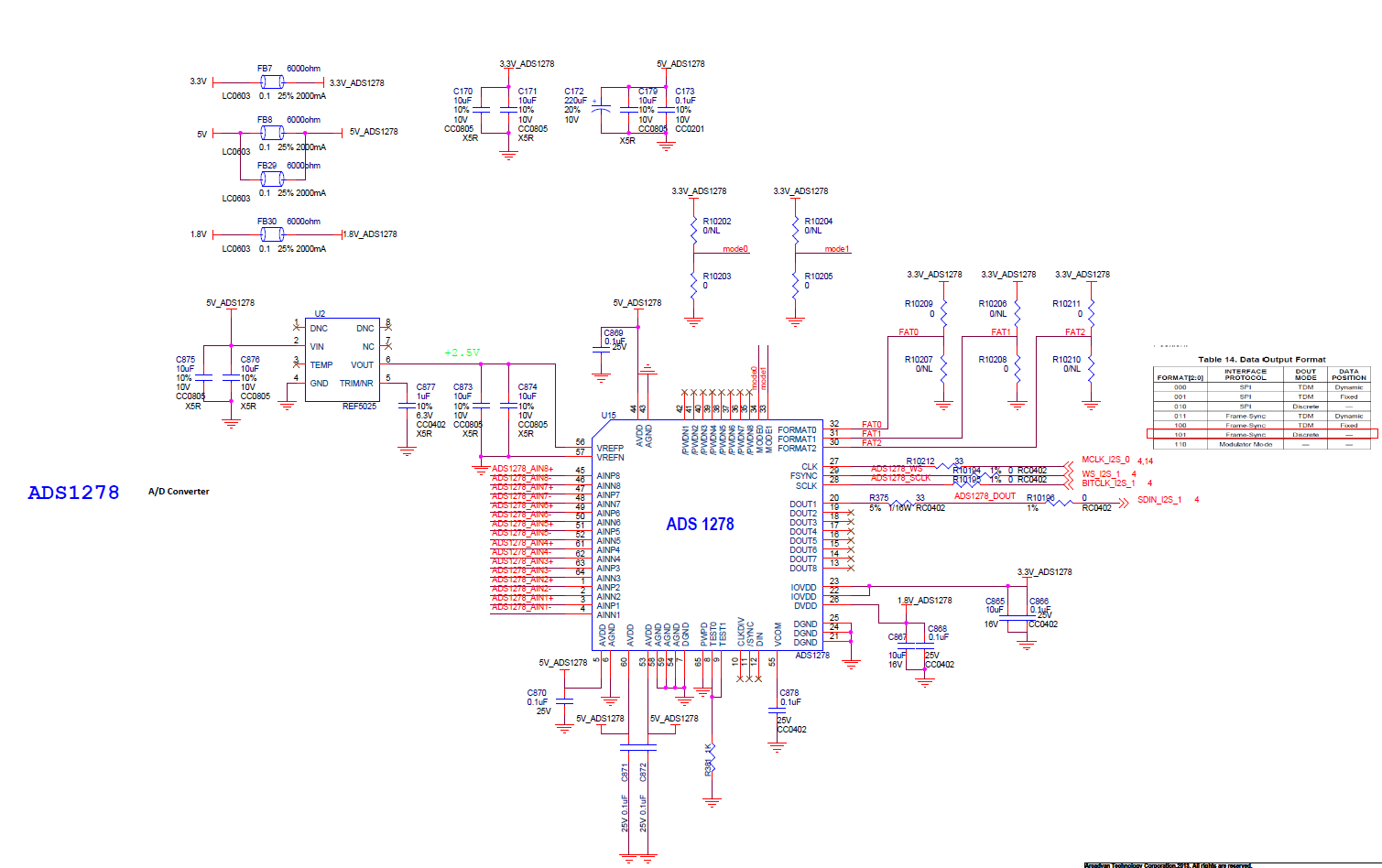

在 客户的新项目中、我们在 ADS1278中进行设计、这是一个好消息。

您可以帮助查看原理图吗?

非常感谢

丹尼

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Denny's:

1. 已检查 ADS1278 引脚排列;一切正常。

2、 AGND 和 DGND 引脚应连接到同一接地层。 如果使用分离的接地平面、则将两个引脚连接到模拟接地。

/PWDNx 引脚必须连接到 DGND 或 IOVDD。 如果所有通道都加电、则将/PWDNx 连接到 IOVDD。

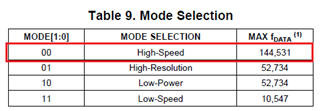

4、 将格式引脚设置为0x101b、这将使用全部8条 DOUT 线路。 如果只需要 DOUT1上的数据、则使用帧同步 TDM、0x011b 或0x100b。 否则、所有 DOUTx 引脚都必须连接到主机 MCU 上的各个输入端。

5. DIN 应连接至 DGND。

6. 必须驱动/SYNC。 强烈建议将/SYNC 连接到主机 MCU 上的 IO 引脚。 该引脚充当复位引脚、建议在上电后发出脉冲、并且所有电源都在建议的工作范围内。 请参阅数据表中的"电源"部分。

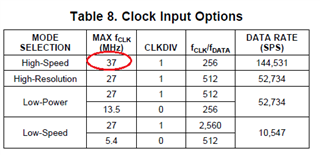

7. 对于模式00 (高速)、CLKDIV 应该被设定为逻辑1。 将 CLKDIV 连接到 IOVDD。

8、 ADC 的 SNR 性能已使用 REF5025和 OPA2350缓冲器进行测试。 REF5025可直接连接到基准输入引脚、但 SNR 和 THD 可能会降级。

此致、

Keith Nicholas

精密 ADC 应用

你好,Nicholas,

感谢您的评论。 我有一些问题需要询问您。

1.已检查 ADS1278引脚排列;一切正常。

Edison:It (爱迪生)还可以。

2、AGND 和 DGND 引脚应连接到同一接地层。

如果使用分离的接地平面、则将两个引脚连接到模拟接地。

Edison:I splits Ground Planes,and connect threes。 请检查。

/PWDNx 引脚必须连接到 DGND 或 IOVDD。 如果所有通道都加电、则将/PWDNx 连接到 IOVDD。

Edison:I connect /PWDN1 to IOVDD,而其他/PWDNx 引脚连接到 DGND

4、将格式引脚设置为0x101b、这将使用全部8条 DOUT 线路。 如果您只需要 DOUT1上的数据、

然后使用帧同步 TDM、0x011b 或0x100b。 否则、所有 DOUTx 引脚都必须连接到主机 MCU 上的各个输入端。

Edison:在我们的用例中,我们将使用 MCLK 22MHz 或24MHz。 如果我们设置0x011b,它是否支持我们的设计?

5. DIN 应连接至 DGND。

Edison:没错。

6.必须驱动/SYNC。 强烈建议将/SYNC 连接到主机 MCU 上的 IO 引脚。

该引脚充当复位引脚、建议在上电后发出脉冲、并且所有电源都在建议的工作范围内。

请参阅数据表中的"电源"部分。

Edison:Add RESET IC (EM6325CXSP5B-2.6)。 请帮助检查原理图。

7.对于模式00 (高速)、CLKDIV 应该被设定为逻辑1。 将 CLKDIV 连接到 IOVDD。

Edison:I connect CLKDIV to IOVDD。

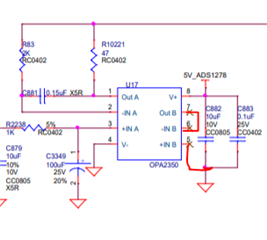

8、ADC 的 SNR 性能已使用 REF5025和 OPA2350缓冲器进行测试。

REF5025可直接连接到基准输入引脚、但 SNR 和 THD 可能会降级。

Edison:我添加了 OPA2350以提高 SNR 和 THD 性能。 请帮助查看我们的原理图。

e2e.ti.com/.../ADS1278-correct-schematic_5F00_0714.pdf

/Edison

您好 Edison、

ADS1278上的 AGND 和 DGND 引脚应连接到模拟接地层。 不要使用电阻器或铁氧体磁珠电感器来分离引脚。 该器件将无法正常工作、更有可能因 ESD 或其他电气过压瞬变而损坏。 接地的原始原理图是正确的。 请确保将两个接地平面连接在一起、并通过此接地平面连接将 IOVDD 和数字 IO 线路布线。 有关正确布局和接地连接的更多详细信息、请参阅此 E2E 帖子。

3、 /PWDN1连接到3.3V、/PWDN2.../PWDN8接地。 在此配置中、仅为通道1供电、所有其他通道 AIN2至 AIN8将关断。 如果您想在 ADS1278中使用8个通道、请将/PWDN2.../PWDN8连接到3.3V。

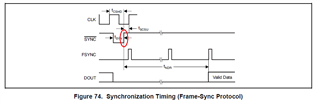

4、 是、模式0x011b 将发送 DOUT1上所有通道的数据、有关详细信息、请参阅数据表中的图79。

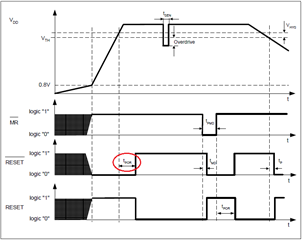

6. 上电复位电路将不工作。 在电源稳定且 ADS1278使能/DRDY (从高电平到低电平的转换)后、/SYNC 引脚应在至少1个 MCLK 周期内驱动为低电平、然后在器件完全复位时返回高电平。 请参阅数据表中的图74。

OPA2350应能正常工作。 不要让 OPA2350上的引脚5和6悬空。 将引脚6连接到引脚7、将引脚5连接到模拟接地。 另一种选择是使用 OPA350。

此致、

Keith

您好,Keith,

感谢您的回复。

2.更正了。

3.I 将 /PWDN2.../PWDN8连接 至3.3V。

4.我选择模式00。 它支持37MHz 的最大频率。 如果我们使用22MHz 或24MHz 作为主时钟。

在此用例中,它是否正确? 或者我们是否需要选择其它模式?

6.e2e.ti.com/.../EM6325CXSP5B_2D00_2.6.pdf

EM6325CXSP5B-2.6是当前使用的复位 IC、其 tPOR 为200ms。

/SYNC 引脚连接到上电复位电路、tPOR 为200ms。

200ms 后,/SYNC 上拉。 然后是 FSYNC 和 DOUT 工作。 不管用吗?

我们希望/SYNC 可以由硬件控制,因此我们不想使用 MCU 上的 IO 引脚

或者您是否有其他建议电路或用于 /sync 的 IC?

8.将 PIN6接至引脚7,引脚5接地。

e2e.ti.com/.../ADS1278-correct-schematic_5F00_0715.pdf

此致。

/Edison

您好 Edison、

4、模式00可以使用22MHz 或24MHz 的时钟。 这是正常的 对于使用 SPI 的所有模式、您可以使用100kHz 至27MHz 范围内的任何时钟频率。 对于模式00和帧同步、您可以使用100kHz 至37MHz 范围内的任何时钟频率。

6. 请给我一天时间仔细检查/SYNC 引脚要求。 我们建议在器件上电后使用脉冲、高->低、然后是低->高。 如果/SYNC 保持低电平、然后在200ms 后转换为低电平->高电平、我不确定该器件将如何响应。

8、 原理图是正确的。

此致、

Keith Nicholas