Other Parts Discussed in Thread: ADS8920B, ADS8922B, ADS8924B

主题中讨论的其他器件: ADS8922B、 ADS8924B

大家好、

我在 ADS892xB 数据表中有关于反冲滤波器设计的问题。 根据数据表、它具有三个采样率。

ADS8920B:1MSPS =1MHz

ADS8922B:500kSPS = 500kHz

ADS8924B:250kSPS = 250kHz

根据我的知识、反冲滤波器的截止频率为采样频率/2。 如果我错了、请纠正我的问题。

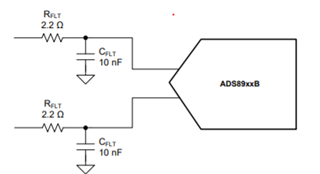

请参阅从数据表获取的下图。 如果我们计算下面给出的 RC 滤波器截止频率

图它是7MHz。 这是所有三种模型采样频率的一半以上。

电阻器值如何变为2.2欧姆

请问我哪里出了问题。

此致

哈里