主题中讨论的其他器件:TI-JESD204-IP、 ADS54J60、 LMK04828、 ADS54J20

您好、TI、

几天前、我联系了 TI 并收到了 TI-JESD204-IP (快速设计 IP)。 我已修改通用 RxTx 环回示例、以使 ZCU102能够通过 J4 HPC1 FMC 连接器从 ADS54J60EVM 接收数据。 我所需的配置如下:

ADC 器件:TI ADS54J60EVM (修订版 D)

JESD204模式:JESD204b 处于子类1模式

在4X 抽取模式下、LMFS = 2221

k = 16 (每多帧的帧数)

采样时钟:1GHz。 逻辑时钟:250MHz

每通道数据位数:16.

线路速率:5Gbps

模式2221/4X 的 LMFC→LMFC =(Fs/4)/K =(1000/4)/16 = 15.625Mhz

SYSREF = LMFC / 8→SYSREF = 1.953125Mhz

我仍然面临 ADC/TI-JESD204-IP 设置问题。 请回答以下问题为荷。

1.提供的 TI Rapid IP 是否支持16位数据通道宽度? 如果没有、我是否必须在正常的32位数据通道宽度模式中仅使用16个最低有效位?

2.我是否应该使用 LMK 配置"LMK_Config_Onboard _1024_MSPS.cfg"和 ADC 配置"ADS54J60_4x_dec_3fs_16_2221.cfg"? 我感兴趣的频率范围为170MHz-200MHz。

3.如何在 ADS54Jxx GUI 中设置所需的 SYSREF 频率?

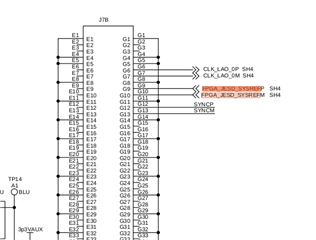

4.在我的设计中、我应该为哪些必要的 FMC 引脚指定限制条件? 例如、FMC 引脚 G9和 G10 (应为 ADC 模块 JESD204b 的 SYSREF 输入)在 ADS54J60EVM Rev. D 原理图中被命名为"FPGA_JESD_SYSREFP"和"FPGA_JESD_SYSREFN"。 这些差分信号是否应该直接来自 LMK04828? SYSREF 信号是如何作为 ZCU102_sysref"输入的源的?

谢谢你。