主题中讨论的其他器件: LMK04832

下午好!

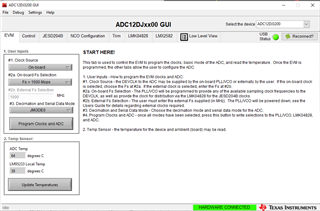

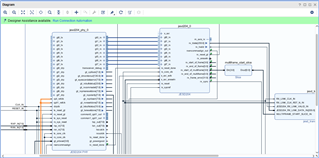

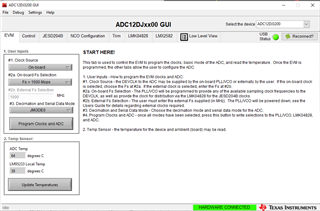

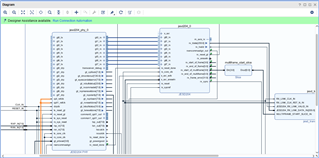

我正在运行 ADC12DJ3200EVM 的 KCU105示例设计。

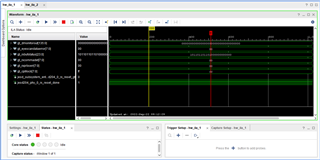

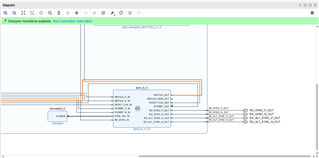

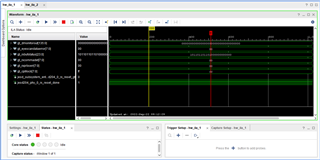

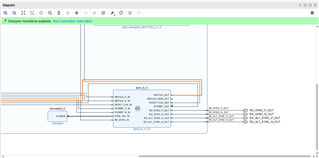

RX 弹性缓冲器似乎正在下溢:

这可能是由什么引起的?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

下午好!

我正在运行 ADC12DJ3200EVM 的 KCU105示例设计。

RX 弹性缓冲器似乎正在下溢:

这可能是由什么引起的?

Nicholas、

此设计由 TI 的第三方供应商完成、该供应商已不再提供。 我强烈建议您考虑向 TI 申请可与这两个平台配合使用的免费 JESD204B IP。 您可以通过访问以下链接申请此 IP JESD204快速设计 IP: https://www.ti.com/tool/TI-JESD204-IP。

目前、JESD204快速设计 IP 支持以下 FPGA 系列:

该 IP 附带了文档和示例参考设计、使用户能够快速上手。

此致、

Jim