器件型号:TSW14J56EVM

尊敬的支持/专家

我正在研究一个项目、将 TSW14J56EVM Arria V FPGA 迁移到 Arria 10。 我知道支持这种迁移不是 TI 的责任、但我认为我可能不是唯一提出这种请求的人。 它可以帮助所有需要使用更新 FPGA 的设计人员。 因此、我想提出任何建议/想法、让这种迁移变得更简单一点、在战场上、退伍军人的一个词可以拯救生命。 这里有几个词可以节省新的一周或一个月的时间。

此致

David

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号:TSW14J56EVM

尊敬的支持/专家

我正在研究一个项目、将 TSW14J56EVM Arria V FPGA 迁移到 Arria 10。 我知道支持这种迁移不是 TI 的责任、但我认为我可能不是唯一提出这种请求的人。 它可以帮助所有需要使用更新 FPGA 的设计人员。 因此、我想提出任何建议/想法、让这种迁移变得更简单一点、在战场上、退伍军人的一个词可以拯救生命。 这里有几个词可以节省新的一周或一个月的时间。

此致

David

示例源代码可从以下链接下载:

https://tidrive.ext.ti.com/u/xdnJpu7ZyZ7X2cmn/fb7b0f39-7b24-4369-9687-90b2483a166a?

TSW14J57当前不支持 AFE58JD48。

您好、Jim、

我认为开发将从将 FPGA 移植到成本更低的 Arria10 (如660)(Intel 开发板 A10_SoC_Devkit_03_31_2016)开始。 因为它来自同一个系列、所以可能不会很困难。 我认为最常见的挑战是该设计的目标是使用 2个或更多 AFE58JD48。 甚至我也非常仔细地研究并理解了 AFE58JD48EVM、但没有提到太多集成和同步多芯片。 在开始设计之前、您能给我一些链接或任何建议、以深入了解更多细节和参考。 对于这样复杂的设计、任何小错误都将耗费数万美元和数周的时间。

顺便说一下、我们是否可以或现实地构建 AFE 板、它具有2个 TX7516和2个 AFE58JD48以及与 TSW14J57EVM 兼容的 FMC 端口。 基于 TI 的 J57平台开发 FPGA 和 PC 软件是否会更简单一些。

感谢你的帮助

此致、

David

David、

链接如下。

Jim

你好、Jim

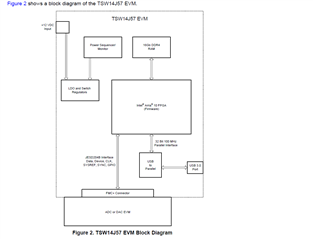

从"TSW14J57 JESD204B 高速数据采集 和图形发生器卡用户指南"(SLWUA,此处是 EMV 方框图。 它与 TSW14J56的架构非常相似。 但是、我从您提供的链接下载的 FPGA 软件包与此架构远不相同。

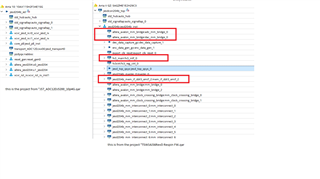

下一张图片是我将两个项目层次并排放置。 在 TSW14J56项目中、有用于 USB3的功能块、如 FX3_main。

用于 DDR 的 DDR3_EMIF。 和 Avalon 桥接器。 但 TSW14J57的项目仅提供 JESD 模块。 和顶级的.v 文件中。 有两 个 altera_jesd204 u0_jesd204模块实例、但有类似这样的注释

" //JESD RX 基本 IP

//JESD Avalon 从设备未使用。 所有从器件信号均处于非活动状态"

作为 JESD 的新手、J56拥有一切、但基于 Arria V、我尝试升级到 Arria10、但并不是很简单。 需要为新芯片创建大量 IP 内核。

J57 EVM 似乎是右侧芯片上的正确示例、但它仅涵盖了电路板功能的一小部分。

我没有想到即插即用示例、但我希望我可以获得尽可能多的方框图等项目。 因此、我可以重点介绍如何应用功能块、而不是学习如何生成每个 IP 以及如何将它们连接在一起。

您能否提供另一个与 J56类似但用于 Arria 10器件的示例项目?

非常感谢!

David

不确定。 试试吧。 也尝试此链接。