主题中讨论的其他器件: OPA2387、 ADS127L01

您好!

下面是有关 ADC 芯片 ADS1278的三个问题。

如下图所示,我想看看我的方法是否可行。 我将差分信号转换为1V 的单模信号、并注入 ADC ADS1278。 信号不能变为负值、因为 OPAM OPA2387是单侧偏置的。 我想确认这种方法是否有效?

2. ADC 将与 Tiva TM4C129 SPI 端口连接,是否可以使用 SYN 引脚来保持 ADC 并在需要时释放以开始转换? 如果不是,如何保持 ADC,然后开始转换?

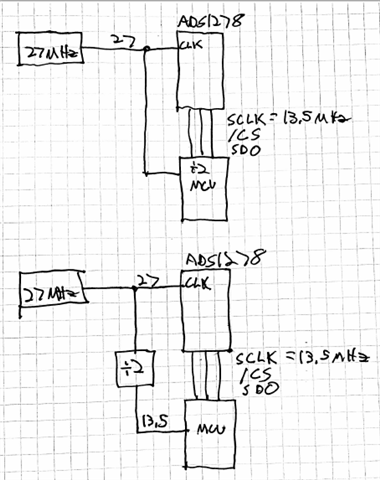

3、SPI 将以控制器提供的10MHz 时钟与 SCLK 引脚上的 ADC 进行通信、同时 ADC 通过 J9连接器连接到自由运行的27MHz 晶体。 ADC 将处于高分辨率模式。 它在高分辨率模式下是否会以这种方式工作?

谢谢