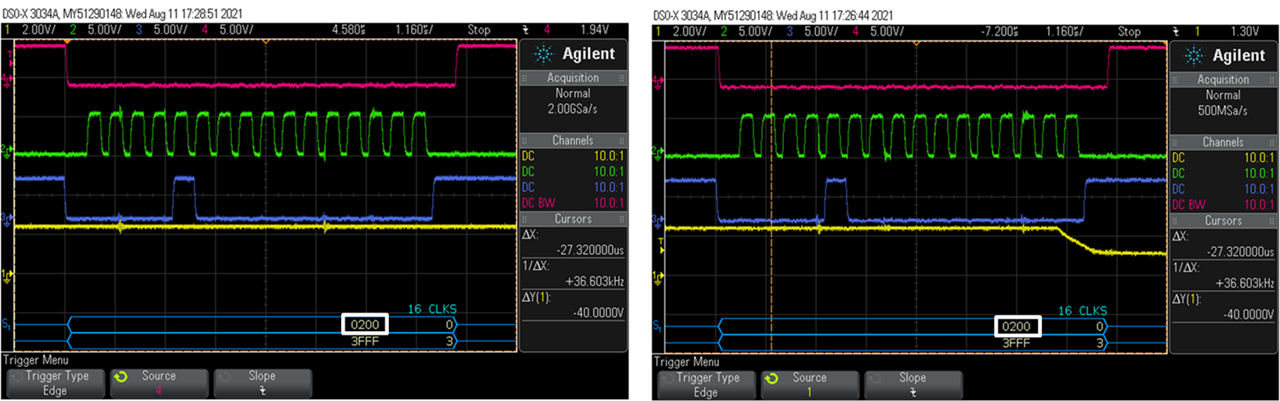

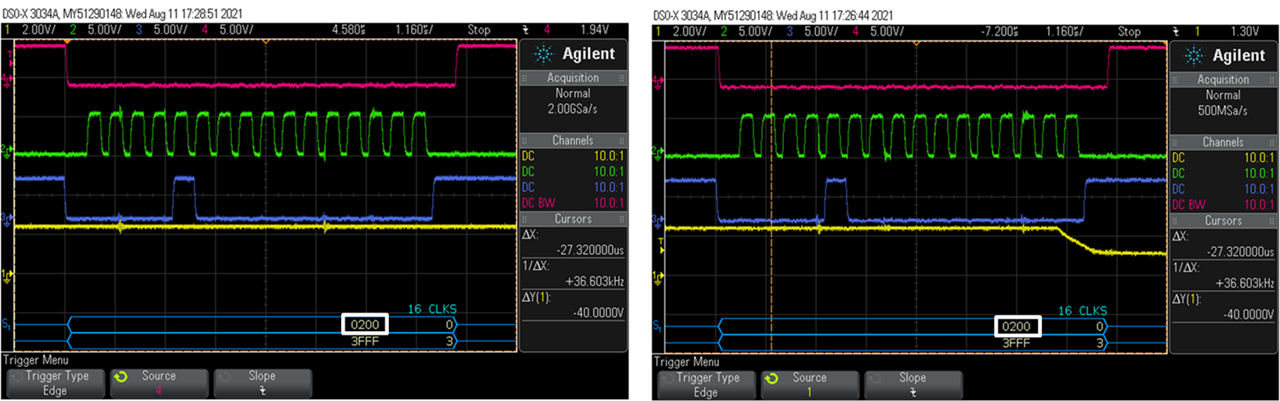

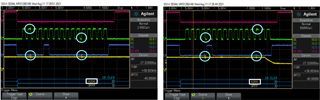

下图是我们收集的正常/异常比较。 两张图片均设置为0200、对应于将数据转换为 VOUT = 2.5V。 但右图中的 DAC VOUT 将突然下降。

当我们写入一个0200并频繁读取时、我们会发现这一点。 那么我们就找不到任何问题了。 但是、当我们经常写入/读取(大约100ms 循环)时、我们可以发现这个问题。 你对此有什么想法吗? 谢谢

右侧的波形不正确。 VOUT 下降、即使寄存器与0200相同。

红色 CS/绿色 SCLK/蓝色 DIN/黄色 DAC VOUT

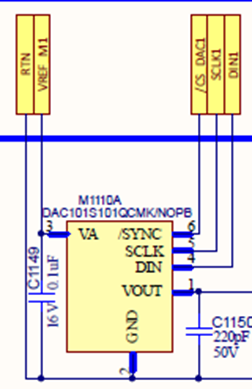

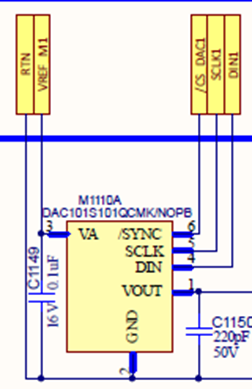

原理图:

BR、Gary

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

下图是我们收集的正常/异常比较。 两张图片均设置为0200、对应于将数据转换为 VOUT = 2.5V。 但右图中的 DAC VOUT 将突然下降。

当我们写入一个0200并频繁读取时、我们会发现这一点。 那么我们就找不到任何问题了。 但是、当我们经常写入/读取(大约100ms 循环)时、我们可以发现这个问题。 你对此有什么想法吗? 谢谢

右侧的波形不正确。 VOUT 下降、即使寄存器与0200相同。

红色 CS/绿色 SCLK/蓝色 DIN/黄色 DAC VOUT

原理图:

BR、Gary

您好、Gary、

在 第15个时钟而不是第16个时钟的下降沿、电压看起来会下降到1.25伏。 这让我认为 DAC 将16位数据解释为0x0400而不是0x0800。 我知道逻辑分析仪正在正确解读数据、您的控制器正在发送正确的数据。

除了验证时序要求、 SCLK、DIN 和 VOUT 上似乎出现周期性干扰。 您是否知道系统中会导致这种情况的原因:

看起来、DAC 有时可能 会将干扰解释为额外的时钟、当在 DIN 上的1之前解释该额外的时钟时、 DAC 解释的实际数据将变为0x0400而不是0x0800 (右移一个)。 10位 DAC 数据将为0x10而不是0x20、这将解释输出电压降低一半的原因。 如果 可能、您能否 关闭导致系统干扰的原因并重新测试对 DAC 的写入? 您还可以尝试向 SCLK 引脚添加一个小电容。

最棒的

Katlynne Jones