您好!

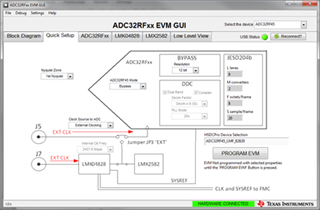

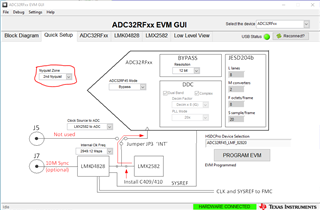

我们的 ADC32RF45EVM 板连接到 FPGA 主板 TSW14J56 (修订版 E)。

具有以下配置:

- fs=3GHz (随 SMA100A 提供的外部时钟:+15dBm 和3GHz 滤波器)

- 该时钟连接到 J5和 J7

- FIN 被过滤(SMA100A RF 发生器)

- 已将引脚调整为-2dBFS

- 2个 Keysight 电源用于电流限制高于5A 的情况

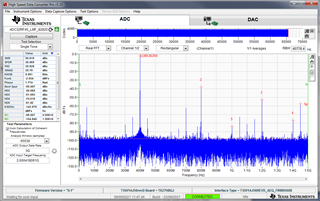

测量以下 SFDR:

- 100MHz:63dBc.

- 900MHz:61dBc.

- 1850MHz:56dBc.

- 2100MHz:50dBc.

- 2600MHz:36dBc.

- 3500MHz:45dBc (-3dBFS & G=-2dB)

您可以看到、我们远离数据表中提供的数字。

我们有2个 ADC32RF45EVM 板、它们都有 SFDR 方面的不良结果。

HD2是限制参数。

我们可以提供 FFT 屏幕截图、文件等...

会导致通道与另一通道略有不同、但与数据表图不符。

ADC32RF45EVM 电路板包括:

- RF45-341

- RF45-333

当使用内部时钟(LMX PLL)时、会获得相似的结果。

您能给我们一种关于这个问题的感觉吗?

此致。